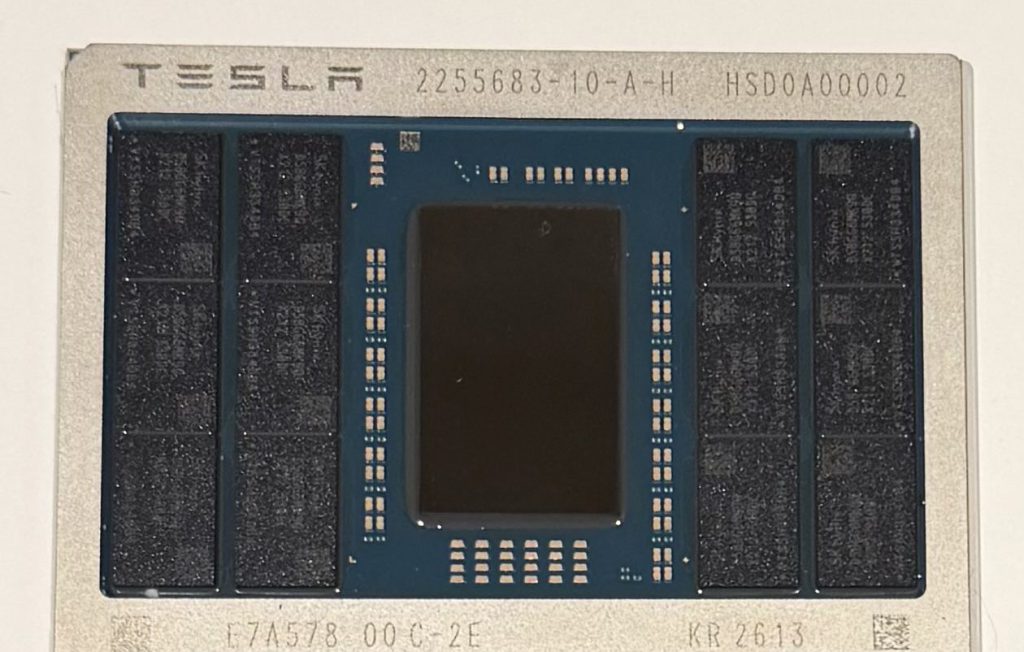

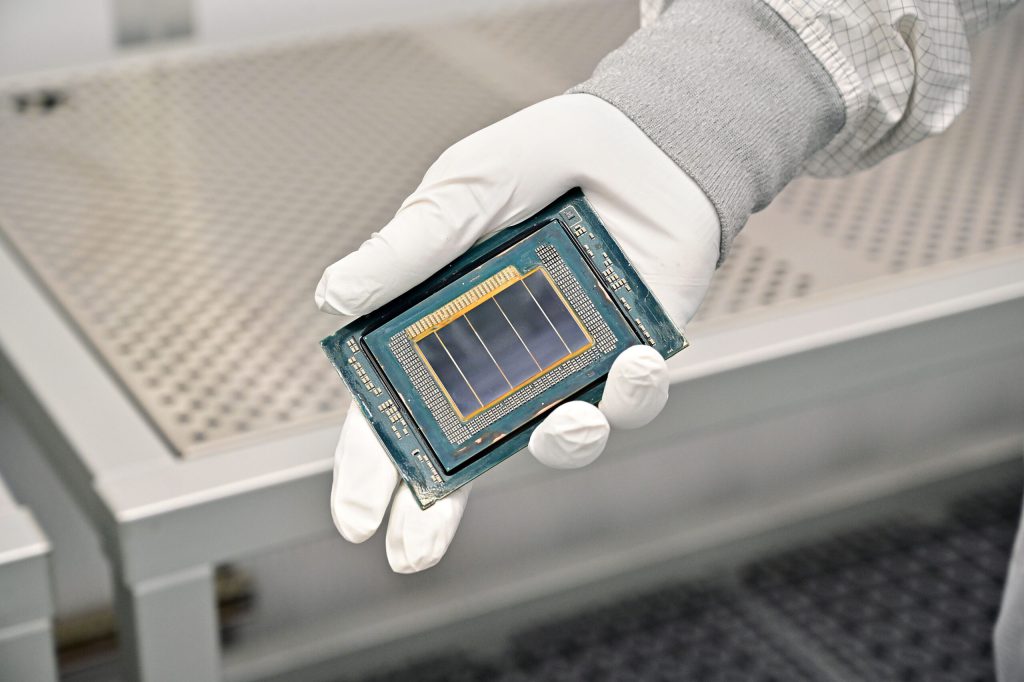

TSMC wyprodukowało pierwszy sprawny układ scalony w procesie technologicznym 3 nm drugiej generacji N3E

Firma Alphawave poinformowała, że wydała jeden z pierwszych w branży chipów wykonanych w technologii N3E firmy TSMC, czyli drugiej generacji procesu technologicznego klasy 3nm. Chip został wyprodukowany przez TSMC i pomyślnie przeszedł wszystkie niezbędne testy. Zostanie on zademonstrowany na forum OIP firmy TSMC jeszcze w tym tygodniu.

Układ, o którym mowa to Alphawave IP ZeusCORE100 1-112Gbps NRZ/PAM4 Serialiser-Deserialiser (SerDes), który obsługuje wiele standardów, które mają być popularne w najbliższych latach. Obejmuje to 800G Ethernet, OIF 112G-CEI, PCIe 6.0 i CXL3.0. SerDes ma obsługiwać bardzo długie kanały, aby umożliwić elastyczne rozwiązania łączności dla serwerów nowej generacji.

“Alphawave jest dumne, że jako jedni z pierwszych wykorzystują najbardziej zaawansowaną technologię 3nm firmy TSMC” – powiedział Tony Pialis, prezes i dyrektor generalny Alphawave. “Nasze partnerstwo kontynuuje wprowadzanie innowacyjnych, szybkich technologii łączności, które zasilą najbardziej zaawansowane centra danych i jesteśmy podekscytowani możliwością zaprezentowania tych rozwiązań na imprezie TSMC OIP Forum.”

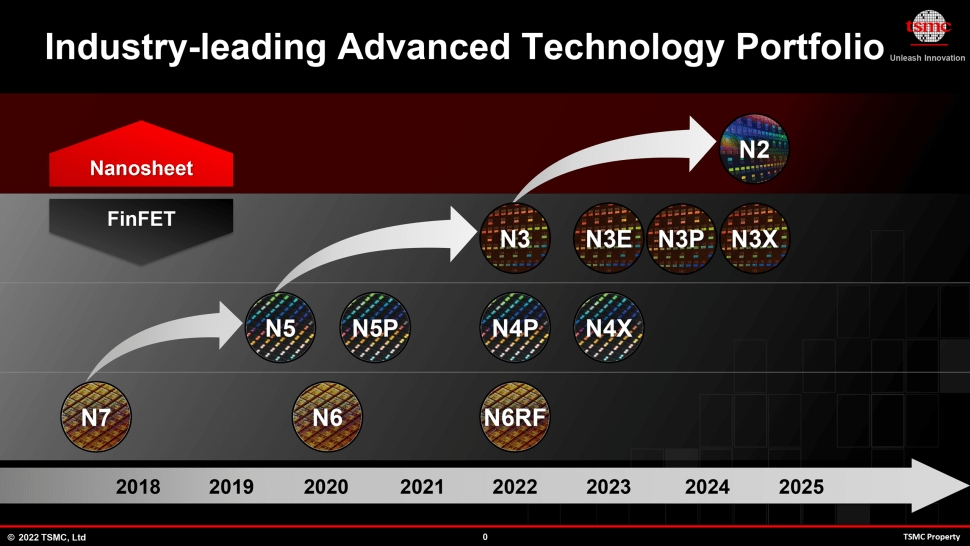

TSMC zamierza wprowadzić pięć technologii procesowych klasy 3nm w ciągu najbliższych dwóch do trzech lat. Pierwsza generacja węzła N3 ma być wykorzystana w kilku projektach przez klientów alfa TSMC (np.: Apple), natomiast druga generacja N3E będzie charakteryzować się ulepszonym procesem, który będzie oferował większy uzysk, wydajność i mniejsze zapotrzebowanie na energię elektryczną.

Oczekuje się, że N3E zostanie przyjęty znacznie szerzej niż N3, ale jego masowa produkcja ma się rozpocząć w połowie lub trzecim kwartale 2023 roku, czyli około rok po tym, jak TSMC zainicjuje produkcję wielkoseryjną z wykorzystaniem swojego węzła produkcyjnego N3.