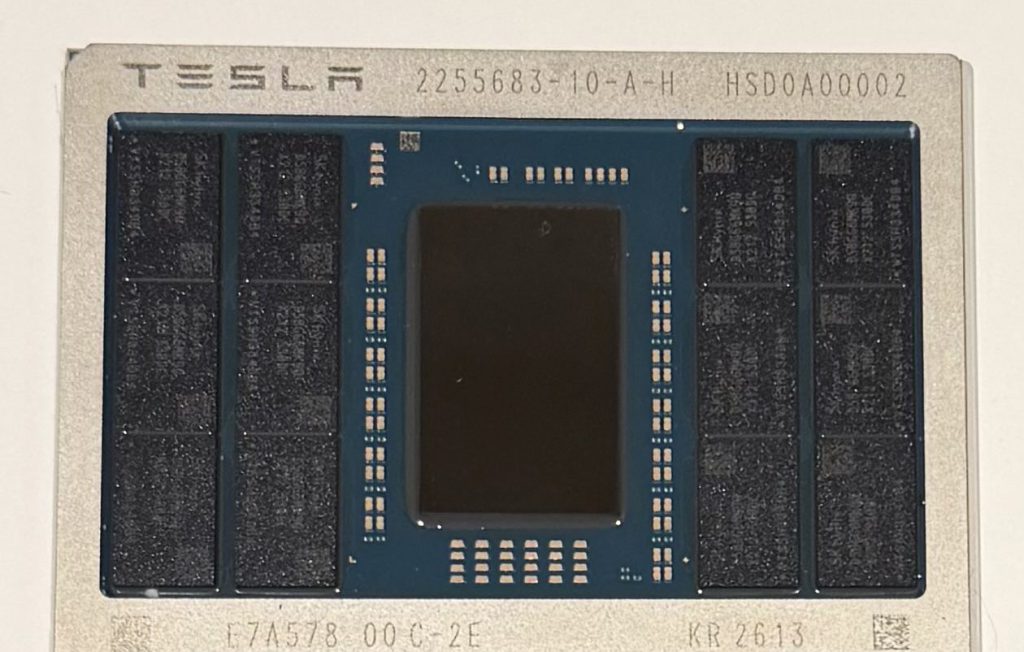

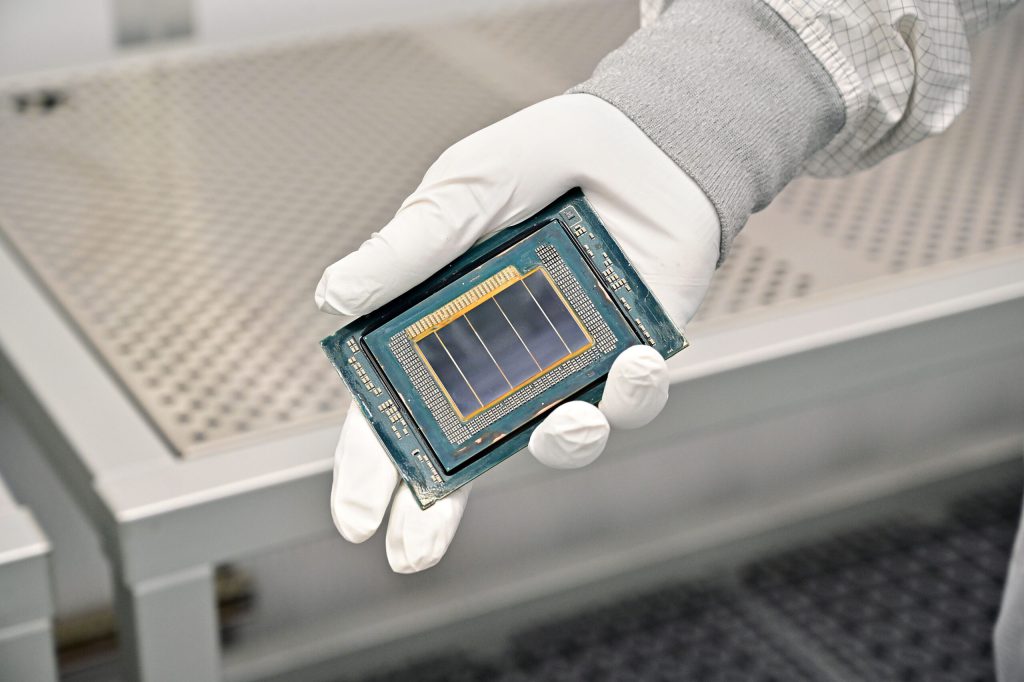

TSMC może obniżyć cenę litografii 3 nm, by przyciągnąć do siebie większą liczbę klientów

Proces technologiczny N3 (klasy 3nm) firmy TSMC przynosi wiele korzyści w zakresie wydajności i mocy, jednak bardzo wysokie koszty początkowego węzła N3 utrudniają jego powszechne przyjęcie. Nie dziwi więc fakt, że według doniesień MyDrivers, firma przygotowuje się do obniżenia cen za produkcję w tym procesie, aby pobudzić zainteresowanie projektantów układów scalonych.

Chociaż w tym momencie wszelkie opublikowane wyceny TSMC na N3 powinny być traktowane jako plotki, jest prawdopodobne, że koszty produkcji TSMC na procesie N3E będą niższe niż na początkowym N3. Nie wiadomo jeszcze, ile firma pobierze za produkcję na innych węzłach klasy N3, takich jak N3P, N3S i N3X. Obniżenie cen produkcji 3nm przyciągnie więcej klientów do tych węzłów, ale nie jest to coś, co stanie się z dnia na dzień.

Początkowa technologia produkcji TSMC N3 (znana również jako N3B) jest podobno używana tylko przez Apple, ponieważ firma jest największym klientem zakładów, który jest skłonny do przyjęcia wiodących węzłów przed innymi. Ale N3 jest kosztowną technologią do wykorzystania. Według China Renaissance proces N3 szeroko wykorzystuje litografię ekstremalnego ultrafioletu (EUV) do 25 warstw, a każdy skaner EUV kosztuje obecnie około 150 – 200 milionów dolarów, w zależności od konfiguracji. Aby zamortyzować zakłady wyposażone w takie narzędzia produkcyjne, TSMC musi pobierać wyższe opłaty za produkcję w swoim procesie N3 i jego następcach.

Niektórzy twierdzą, że TSMC może pobierać nawet 20 000 dolarów za wafel N3 – w porównaniu do 16 000 dolarów za wafel N5 – i chociaż takie wyceny zależą od wielu czynników, kluczowym wnioskiem jest to, że produkcja układów scalonych staje się coraz droższa. Wzrost kosztów oznacza mniejsze zyski dla firm takich jak AMD, Broadcom, MediaTek, Nvidia i Qualcomm, dlatego też twórcy układów scalonych ponownie rozważają sposób tworzenia zaawansowanych projektów i korzystania z wiodących węzłów.

“Uważamy, że znaczący wzrost [N3] nastąpi w drugiej połowie 2023 roku, kiedy będzie gotowa zoptymalizowana wersja, N3E” – napisał Szeho Ng, analityk z China Renaissance. “Jego główni klienci z branży HPC (np. AMD, Intel), smartfonów (np. QCOM, MTK) i ASIC (np. MRVL, AVGO, GUC) prawdopodobnie pozostaną przy N4/5 i wybiorą N3E jako swój pierwszy krok w klasie N3. Tymczasem uważamy, że adopcja podstawowej klasy N3 (aka N3B) będzie w dużej mierze ograniczona do produktów Apple.”

Aby zachęcić swoich partnerów do korzystania z technologii technologicznych klasy N3, TSMC podobno rozważa obniżenie cen za te węzły. W szczególności, proces N3E firmy TSMC wykorzystuje EUV tylko do 19 warstw i charakteryzuje się nieco mniejszą złożonością w zakresie produkcji, a zatem jest tańszy w użyciu. TSMC mogłoby obniżyć ceny produkcji N3E bez szkody dla rentowności firmy.