432-rdzeniowy układ RISC-V zbudowany na zasadzie chipletu, jest już prawie gotowy do wprowadzenia na rynek

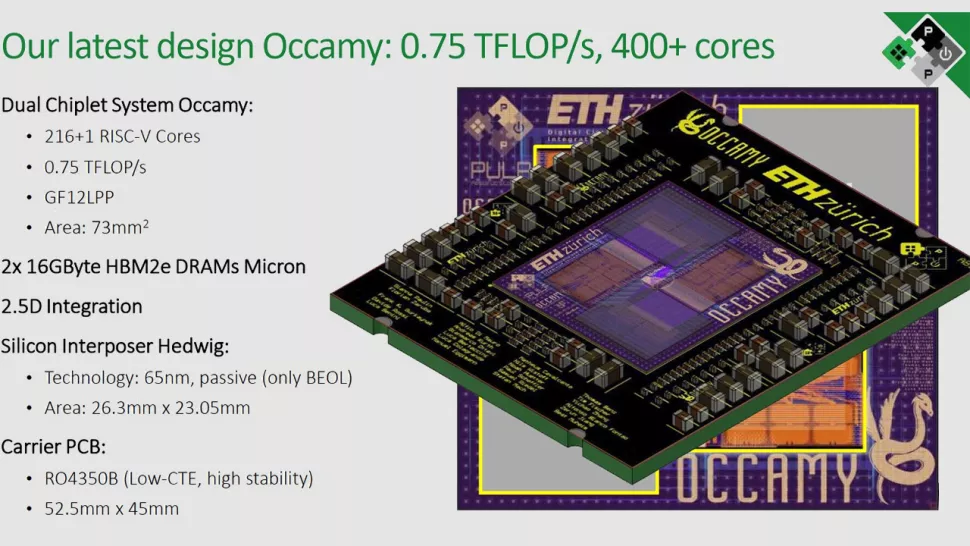

Procesor Occamy wykorzystuje architekturę chipletów i umieszcza w nim 432 akceleratory RISC-V i AI oraz został wyposażony w 32 GB pamięci HBM2Eł. Układ jest wspierany przez Europejską Agencję Kosmiczną i opracowany przez inżynierów z ETH Zürich i Uniwersytetu w Bolonii, jak donosi HPC Wire.

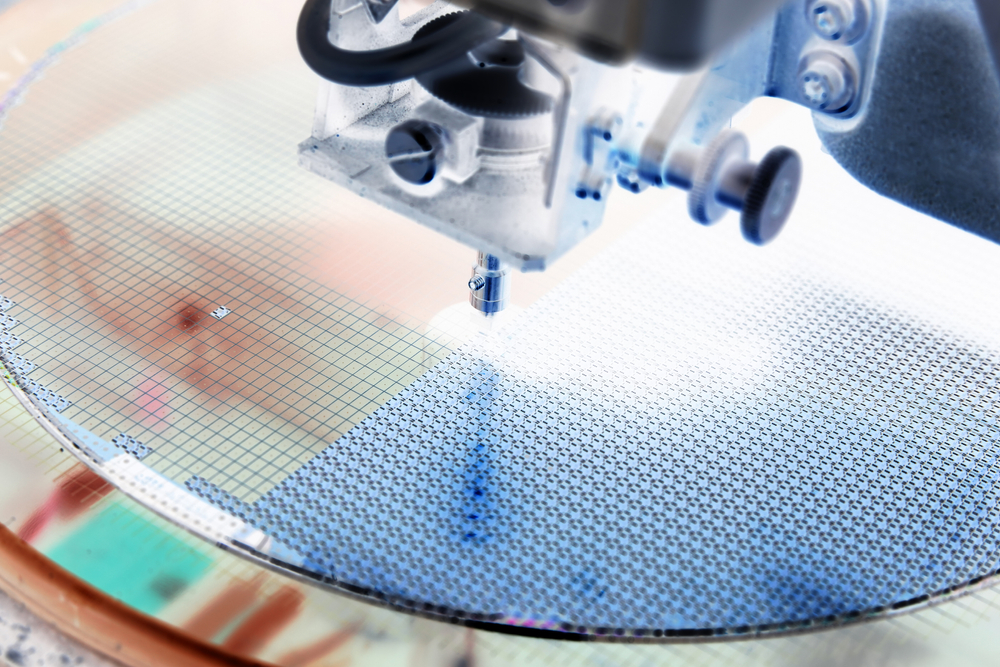

Wspierany przez ESA procesor Occamy wykorzystuje dwa układy scalone z 216 32-bitowymi rdzeniami RISC-V, nieznaną liczbą 64-bitowych jednostek FPU do obliczeń macierzowych i wykorzystuje dwa pakiety pamięci HBM2E o pojemności 16 GB od firmy Micron. Rdzenie są połączone za pomocą krzemowego interpozytora, a dwupłytkowy procesor może zapewnić 0,75 FP64 TFLOPS wydajności i 6 FP8 TFLOPS możliwości obliczeniowych.

Ani ESA, ani jej partnerzy nie ujawnili zużycia energii przez procesory Occamy, ale mówi się, że układ może być chłodzony pasywnie, co oznacza, że może to być procesor o niskim poborze mocy.

Każdy chiplet Occamy ma 216 rdzeni RISC-V i matrycowe FPU, w sumie około miliarda tranzystorów rozłożonych na 73mm^2 krzemu. Płytki są wykonane przez GlobalFoundries przy użyciu jej procesu produkcyjnego 14LPP.

Chiplet o powierzchni 73mm^2 nie jest szczególnie dużą matrycą. Dla przykładu, Alder Lake Intela (z sześcioma wydajnymi rdzeniami) ma matrycę o wielkości 163 mm^2. Jeśli chodzi o wydajność, to GPU A30 Nvidii z 24 GB pamięci HBM2 zapewnia 5,2 FP64/10,3 FP64 Tensor TFLOPS, a także 330/660 ( z rozproszeniem) INT8 TOPS.

Tymczasem jedną z zalet konstrukcji chipletowych jest to, że ESA i jej partnerzy z ETH Zürich i Uniwersytetu w Bolonii mogą w razie potrzeby dodać do pakietu inne chiplety, aby przyspieszyć określone obciążenia robocze.

Procesor Occamy został opracowany w ramach programu EuPilot i jest jednym z wielu chipów, które ESA rozważa do obliczeń w lotach kosmicznych. Nie ma jednak gwarancji, że proces ten rzeczywiście zostanie wykorzystany na pokładach statków kosmicznych.

Projekt Occamy ma na celu wsparcie obliczeń o wysokiej wydajności i obciążeń AI poprzez uruchomienie bare-metal, ale nie jest jeszcze jasne, czy działanie będzie na poziomie kontenera, czy na poziomie bare-metal. Procesor Occamy może być emulowany na układach FPGA. Implementacja została przetestowana na dwóch układach FPGA AMD Xilinx Virtex UltraScale+ HBM oraz na układzie FPGA Virtex UltraScale+ VCU1525.