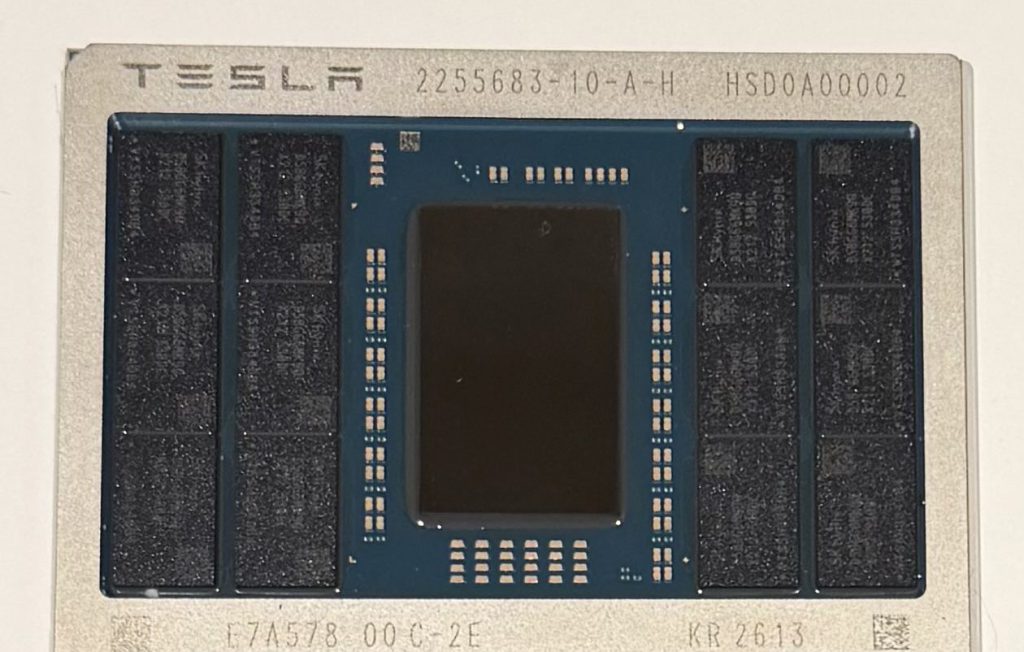

TSMC zapowiada produkcję HBM4 nowej generacji z węzłami 12 nm i 5 nm

Podczas prezentacji TSMC na Europejskim Sympozjum Technologicznym 2024, które odbyło się 14 maja, firma ujawniła nowe szczegóły dotyczące matryc bazowych, które wyprodukuje dla HBM4 przy użyciu zaawansowanych procesów logicznych.

Z raportu AnandTech wynika, że TSMC planuje wykorzystać węzły procesowe 12 nm i 5 nm do produkcji najnowszej pamięci HBM4.

Cytując kierownictwo TSMC, największa na świecie wyspecjalizowana odlewnia półprzewodników zastosowała dwa procesy produkcyjne, N12FFC+ i N5, aby zintegrować pamięć HBM4E z procesorami AI i HPC nowej generacji.

Według starszego dyrektora ds. projektowania i platformy technologicznej, przywoływanego w raporcie, TSMC współpracuje obecnie z partnerami HBM zajmującymi się pamięcią, w tym Micronem, Samsungiem i SK Hynix, nad zaawansowanymi węzłami ukierunkowanymi na HBM4.

Wcześniej, w połowie kwietnia, firma SK Hynix ogłosiła, że podpisała protokół ustaleń z TSMC w sprawie współpracy przy produkcji HBM nowej generacji oraz ulepszaniu logiki i integracji HBM poprzez zaawansowaną technologię pakowania. W ramach tej inicjatywy firma planuje kontynuować prace nad HBM4, który ma być produkowany masowo od 2026 roku.

Oczekuje się, że N12FFC+, uważany za bardziej opłacalny, zapewni wydajność HBM, podczas gdy podstawowa matryca N5 może zapewnić więcej logiki przy znacznie niższej mocy.

Na sympozjum firma TSMC stwierdziła, że stosowany przez nią proces 12FFC+ dobrze nadaje się do wydajności HBM4, umożliwiając dostawcom pamięci budowanie stosów 12-Hi (48 GB) i 16-Hi (64 GB), przy przepustowości na stos przekraczającej 2 TB/s . Optymalizuje także CoWoS-L i CoWoS-R dla HBM4, które wykorzystują ponad osiem warstw do obsługi routingu ponad 2000 połączeń wzajemnych przez HBM4 z odpowiednią integralnością sygnału.

Mówi się, że te rozwiązania w zakresie opakowań zapewniają przekładki, które mogą pomieścić do 8 razy większy rozmiar siatki, zapewniając wystarczającą ilość miejsca dla aż 12 stosów pamięci HBM4. Ponadto matryce podstawowe wyprodukowane w procesie N5 będą charakteryzowały się zwiększoną gęstością logiczną, niższym zużyciem energii i zwiększoną wydajnością.

Jednak najbardziej znaczącą zaletą mogą być wyjątkowo małe odstępy między połączeniami, jakie można uzyskać przy tak zaawansowanej technologii procesowej, wynoszące od 6 do 9 mikronów. Ta opcja umożliwi łączenie matryc podstawowych N5 z bezpośrednim łączeniem, ułatwiając układanie 3D HBM4 bezpośrednio na chipach logicznych. Z raportu wynika, że bezpośrednie łączenie może znacznie zwiększyć wydajność pamięci, co jest kluczowym ulepszeniem w przypadku układów AI i HPC, które stale wymagają większej przepustowości pamięci.