Samsung planuje wprowadzić usługę pakowania chipów 3D HBM jeszcze w 2024 roku

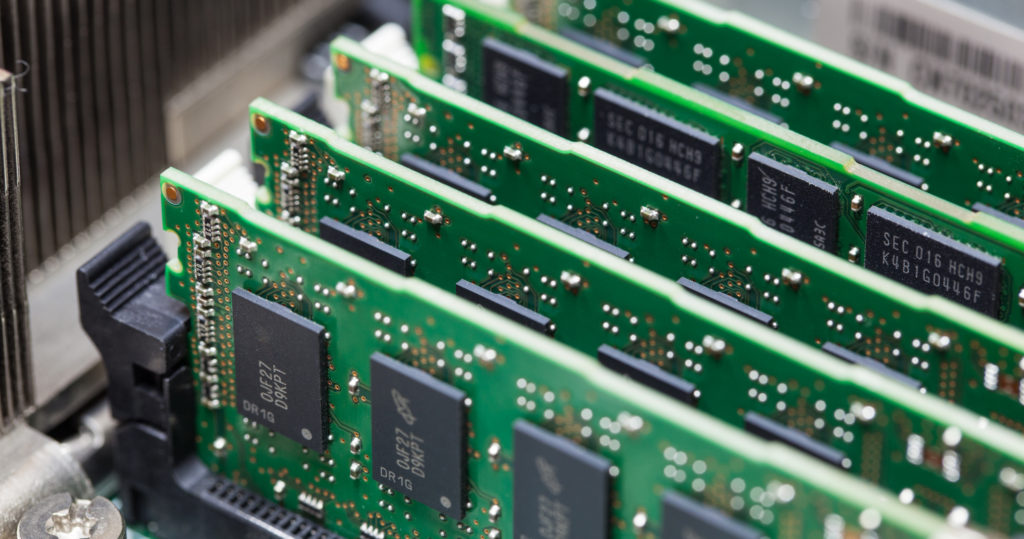

W 2023 roku Samsung ujawnił plany wprowadzenia na rynek zaawansowanej technologii trójwymiarowego (3D) pakowania chipów, która byłaby w stanie zintegrować pamięć i procesory potrzebne do tworzenia chipów o wysokiej wydajności, w znacznie mniejszych rozmiarach.

Jak wynika z doniesień mediów koreańskich, podczas czerwcowego Forum Odlewniczego Samsung w San Jose gigant technologiczny ogłosił, że jeszcze w tym roku wprowadzi dla HBM usługi pakowania 3D.

Na razie chipy HBM są w większości wyposażone w technologię 2,5D. Powołując się na źródła branżowe oraz personel firmy Samsung, oczekuje się, że opracowana przez firmę technologia pakowania chipów 3D trafi na rynek dla HBM4, szóstej generacji rodziny HBM.

Ogłoszenie firmy Samsung dotyczące planu działania dotyczącego pakowania 3D HBM zostało podane po tym, jak dyrektor generalny firmy NVIDIA, Jensen Huang, ujawnił Rubin na targach COMPUTEX 2024, nadchodzącej architekturze platformy AI firmy po Blackwell.

Według doniesień procesor graficzny Rubin będzie wyposażony w 8 układów HBM4, a procesor graficzny Rubin Ultra będzie wyposażony w 12 układów HBM4, a premiera planowana jest na rok 2026.

Obecnie platforma SAINT (Samsung Advanced Interconnect Technology) firmy Samsung obejmuje trzy typy technologii układania stosów 3D: SAINT S, SAINT L i SAINT D. SAINT S polega na układaniu pionowo pamięci SRAM na układach logicznych, takich jak procesory, podczas gdy SAINT L polega na układaniu układów logicznych na innych układach logicznych lub procesorach aplikacyjnych (AP). Z drugiej strony SAINT D wymaga pionowego układania pamięci DRAM z układami logicznymi, takimi jak procesory i procesory graficzne.

Korea Economic Daily zauważył, że w przeciwieństwie do technologii 2,5D, w której chipy HBM są poziomo połączone z procesorem graficznym na krzemowej przekładce, poprzez ułożenie chipów HBM pionowo na procesorze graficznym, pakowanie 3D może jeszcze bardziej przyspieszyć uczenie się danych i przetwarzanie wnioskowań, a tym samym nie wymaga silikonowej przekładki, cienkiego podłoża umieszczanego pomiędzy chipami, aby umożliwić im komunikację i współpracę.

Jak podaje wzmiankowany periodyk, Samsung planuje oferować opakowania 3D HBM pod klucz. Aby to osiągnąć, jego zaawansowany zespół zajmujący się pakowaniem połączy pionowo chipy HBM produkowane przez dział pamięci z procesorami graficznymi montowanymi dla firm bez technologii fabless przez jego odlewnię, jak zauważono w raporcie.

Jeśli chodzi o wieloletniego rywala firmy Samsung, firmę TSMC, jej chip on Wafer on Substrate (CoWoS) odegrał kluczową rolę w rewolucji AI, umożliwiając klientom pakowanie większej liczby rdzeni procesorów i stosów HBM obok siebie na jednym przekładkach.