AMD ujawnia EPYC „Venice” – pierwszy procesor HPC w litografii 2 nm TSMC

AMD potwierdziło zakończenie fazy „tape-out” nowej generacji procesorów EPYC „Venice”, opartych na architekturze Zen 6 i wykonanych w technologii 2 nm TSMC. To nie tylko technologiczny krok milowy, ale również sygnał o zaostrzającej się rywalizacji na rynku centrów danych.

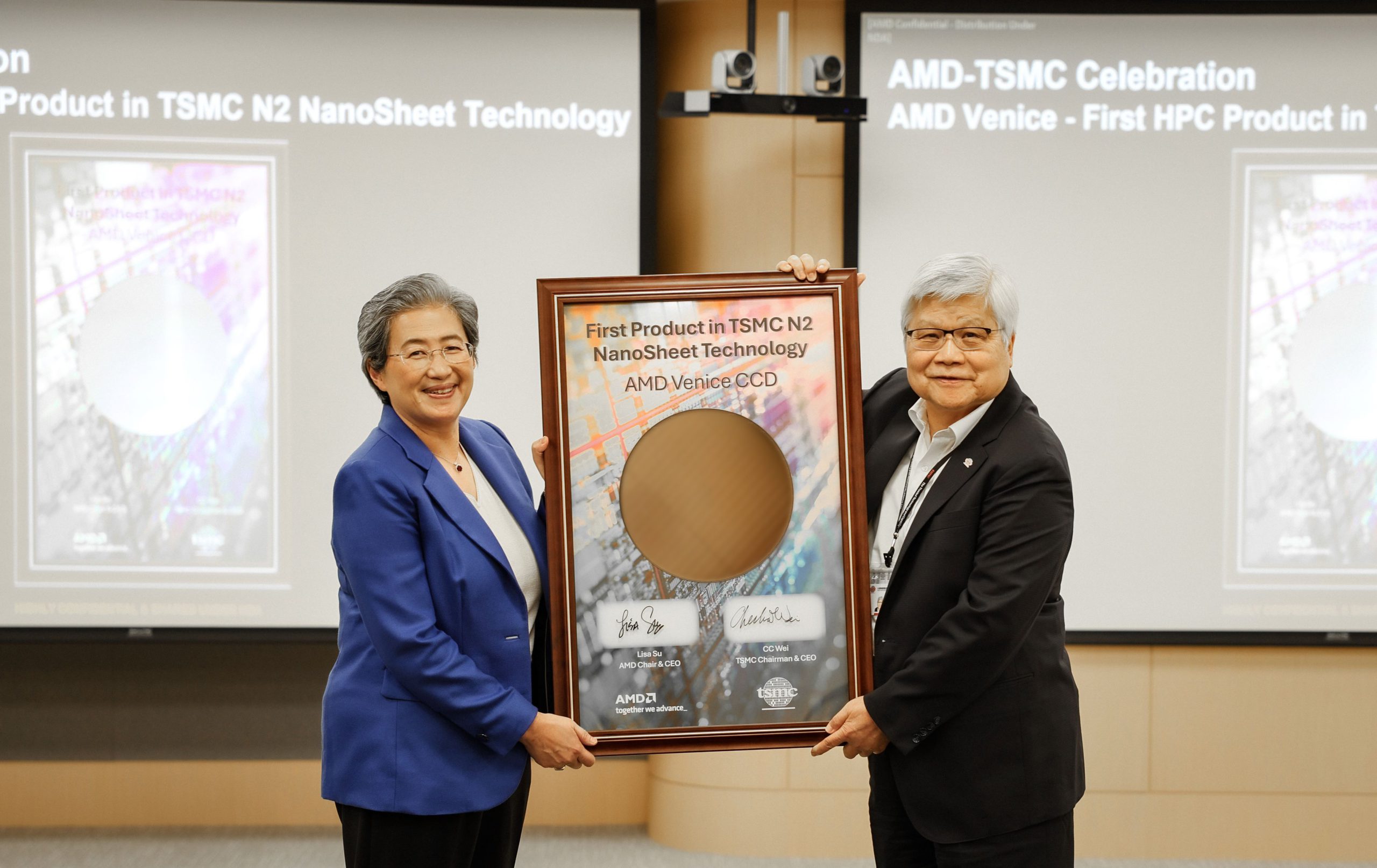

AMD i TSMC wspólnie ogłaszają przełomowy moment w historii przetwarzania danych – pierwszy procesor serwerowy EPYC „Venice”, oparty na architekturze Zen 6 i wyprodukowany w litografii 2 nm (N2), zakończył etap tape-out. Oznacza to, że projekt chipu został ukończony i przekazany do finalnych testów produkcyjnych. Nowy układ trafi do produkcji seryjnej w przyszłym roku, wzmacniając pozycję AMD w sektorze wysokowydajnych obliczeń (HPC).

Platforma „Venice” to szósta generacja procesorów serwerowych EPYC i pierwsza, która korzysta z nowego gniazda SP7 oraz obsługuje 12 lub 16 kanałów pamięci DDR5 – co znacząco zwiększa przepustowość i skalowalność systemów. Nowa architektura, bazująca na rdzeniach Zen 6 i Zen 6c, ma przynieść wzrost wydajności oraz efektywności energetycznej, choć szczegóły techniczne nie zostały jeszcze ujawnione.

TSMC pozycjonuje proces 2 nm jako kluczowy krok w dalszym rozwoju miniaturyzacji i energooszczędności układów scalonych. Wspólne świętowanie sukcesu przez AMD i TSMC podkreśla rosnącą rolę strategicznej współpracy obu firm.

Dr Lisa Su, prezes AMD, zaznaczyła, że dzięki głębokiej integracji zespołów R&D oraz produkcyjnych z TSMC, firma może dostarczać innowacyjne rozwiązania na czoło branży HPC.

„Bycie głównym klientem TSMC dla procesu N2 oraz dla fabryki w Arizonie to dowód na nasze zaangażowanie w rozwój przyszłości obliczeń,” – powiedziała Su.

Warto zauważyć, że równolegle AMD potwierdziło pomyślne uruchomienie i walidację 5. generacji EPYC w nowym zakładzie TSMC w Arizonie.

Zdaniem dr. C.C. Wei, prezesa TSMC, współpraca z AMD umożliwia rozwój przełomowych technologii krzemowych:

„Wspólnie osiągamy lepszą wydajność, efektywność energetyczną i uzyski w produkcji układów HPC nowej generacji.”