Computex 2021: AMD potwierdza, że przed układami Zen 4 zobaczymy układy budowane warstwowo – z pamięcią cache układaną w stosy.

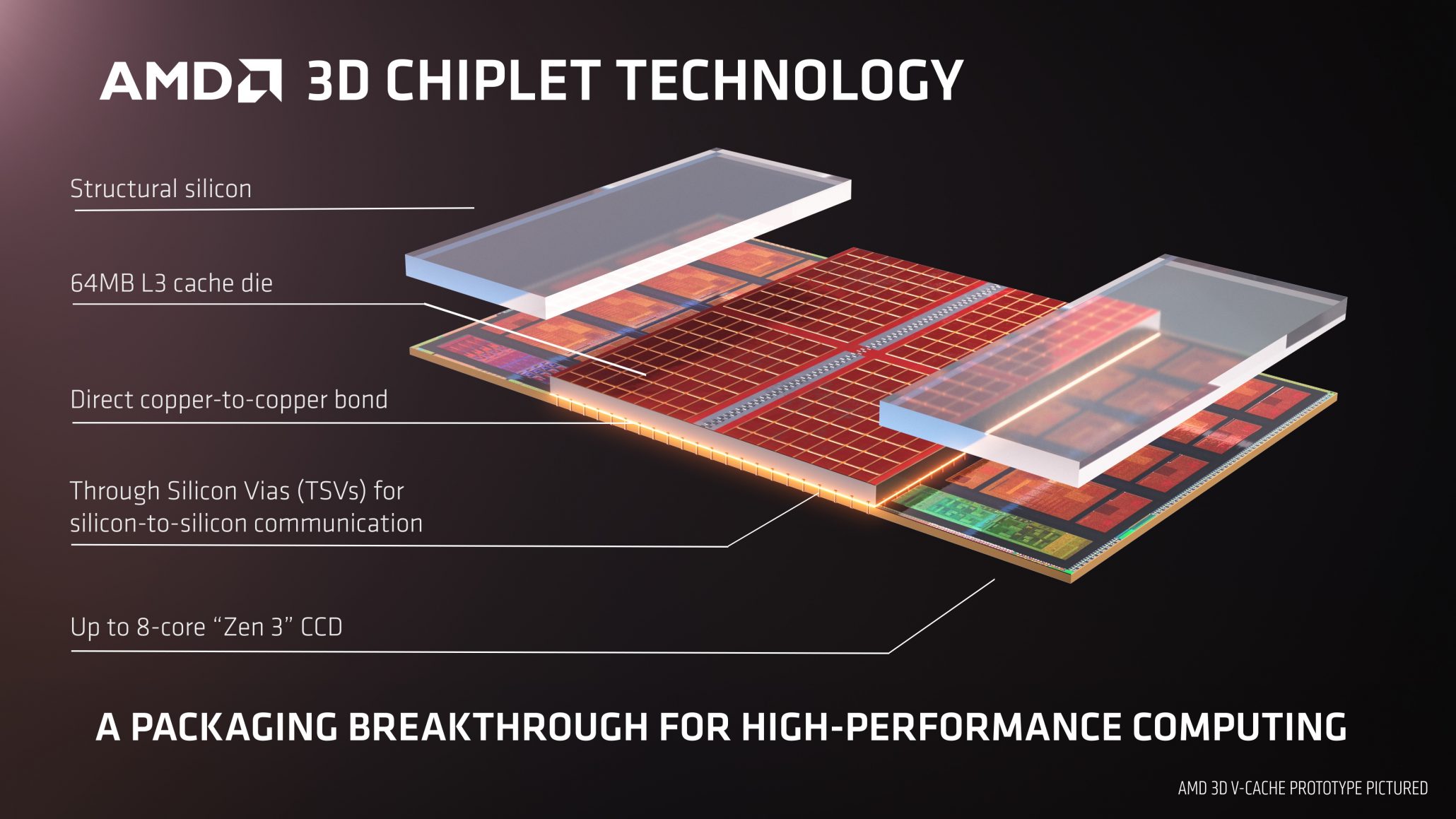

AMD potwierdziło, że technologia 3D V-Cache Stack Chiplet, zostanie wprowadzona w procesorach Ryzen Zen 3 na początku przyszłego roku.

AMD potwierdziło, że technologia 3D V-Cache zostanie skierowana do układów Zen 3. Architektura Zen 3 jest już od jesieni ubiegłego roku dostępna w procesorach AMD Ryzen, ale producent planuje wykorzystać tę architekturę w swoich pierwszych układach warstwowych. Według zapowiedzi AMD, procesory te zostaną wyprodukowane jeszcze w tym roku, więc możemy spodziewać się prawdziwej, rynkowej premiery, gdzieś na początku 2022 roku.

Nie podano przy tym, czy będą to procesory stacjonarne czy mobilne. Chociaż chyba możemy założyć, że podobną technologię AMD wykorzysta w obu tych zastosowaniach, chociaż nie od razu. Inne szczegóły potwierdzają, że pojedynczy stos 3D V-Cache zawiera 64 MB pamięci podręcznej L3. Pamięć podręczna zostanie w ten sposób dodana do istniejących 32 MB pamięci podręcznej L3, co łącznie da 96 MB na jeden blok CCD. Jeśli będzie to więc np. układ składający się z dwóch bloków CCD, z jednym stosem 3D V-Cache na chiplet, układ będzie miał łącznie 192 MB pamięci podręcznej. Jednak AMD twierdzi, że stos V-Cache może wzrosnąć do 8-hi (8 warstw), co oznacza, że pojedynczy CCD może technicznie zaoferować do 512 MB pamięci podręcznej L3 oprócz 32 MB pamięci podręcznej na samym CCD Zen 3.

Warstwowe budowanie układów elektronicznych nie jest rzeczą niespotykaną – rok temu wprowadził je Intel w układach Lakefield… których jednak nie zobaczyliśmy zbyt wiele.

https://itreseller.pl/computex-2021-jexynos-rdna2/