Computex 2024: AMD zapowiada 5. generację procesorów serwerowych EPYC “Turin”

Podczas keynote’u na targach Computex 2024, prezes AMD Lisa Su ogłosiła, że długo wyczekiwane procesory 5. generacji EPYC Turin zadebiutują w drugiej połowie 2024 roku.

Na piątą generację EPYC’ów rzeczywiście przyszło sporo poczekać, jednak, zgodnie z zapowiedzią, zobaczymy je na rynku do końca tego roku. Te 3nm chipy wprowadzą architekturę Zen 5 do świata centrów danych, a AMD twierdzi, że będą one do 5,4 razy szybsze od konkurencyjnych procesorów Xeon firmy Intel w kluczowych obciążeniach AI.

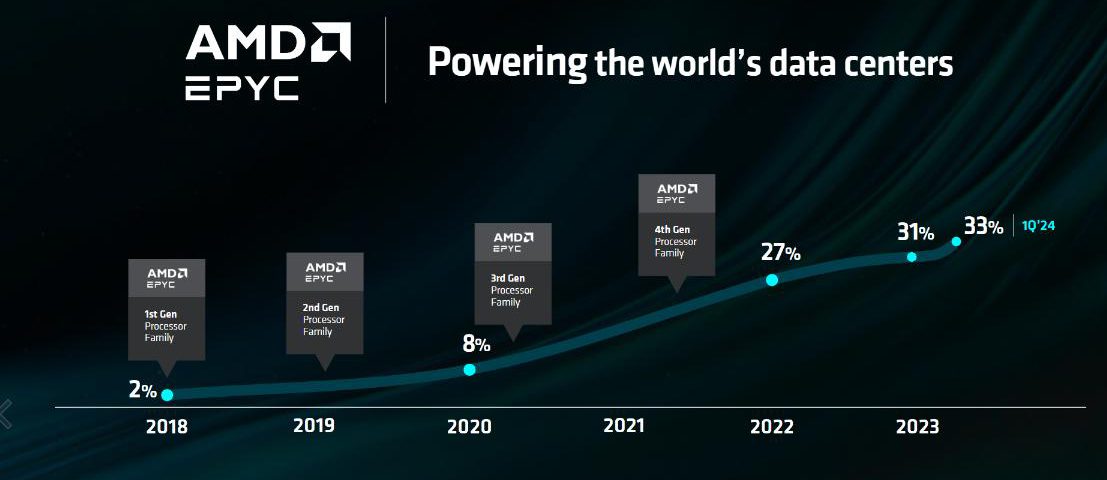

Procesory o kodowej nazwie Turin będą dostępne w dwóch wariantach: jeden z maksymalnie 128 standardowymi rdzeniami Zen 5 i drugi z rdzeniami zoptymalizowanymi pod kątem gęstości, nazywanymi Zen 5c, który będzie oferował aż do 192 rdzeni. Lisa Su ogłosiła również, że AMD odpowiada obecnie za 33% rynku centrów danych.

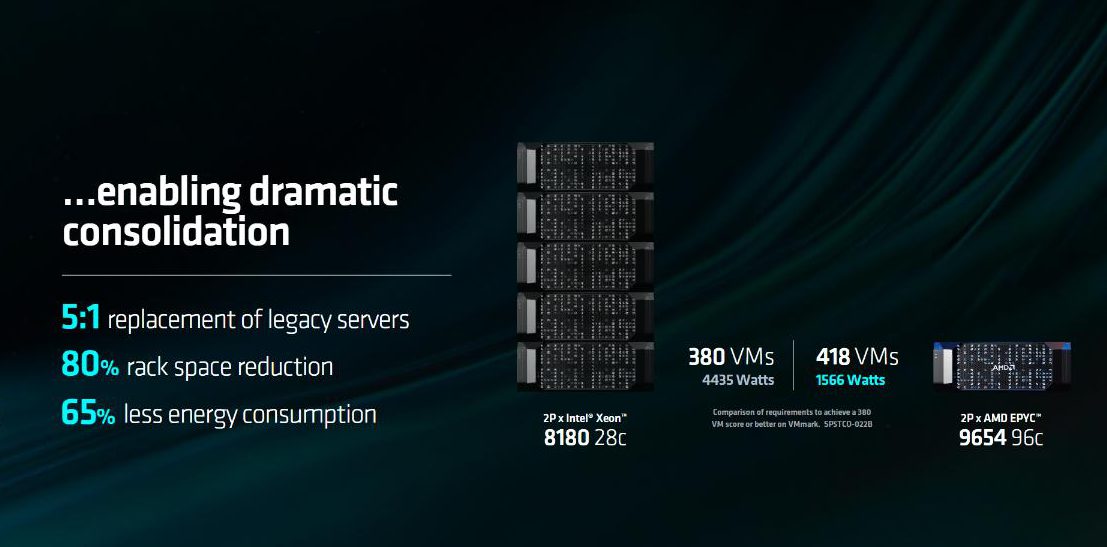

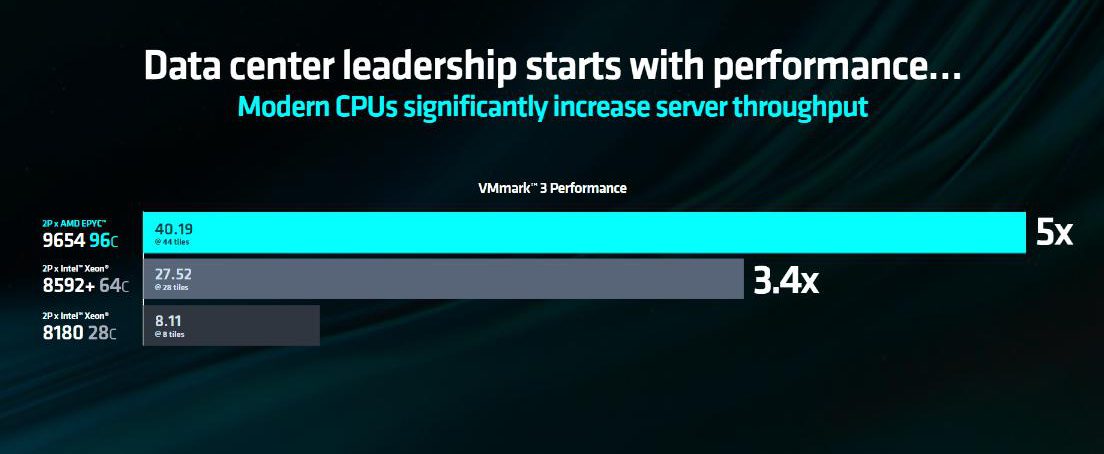

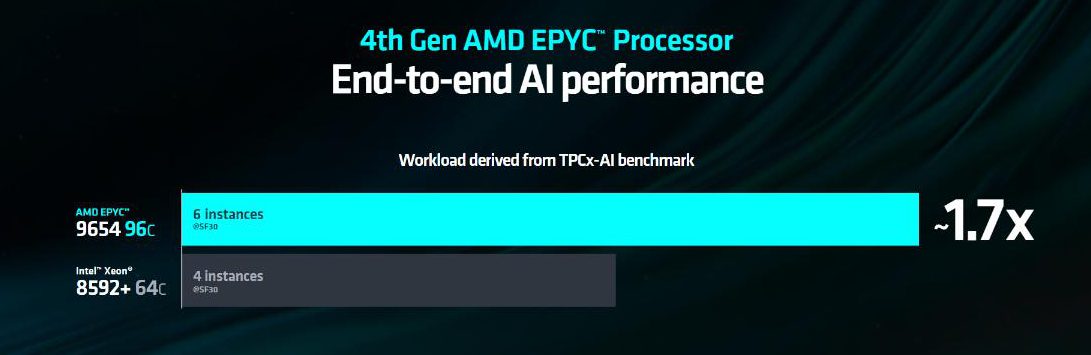

AMD zaprezentowało szereg benchmarków porównujących nowe procesory z konkurencyjnymi chipami Intela. Według AMD, procesory Turin osiągają do 5,4 razy lepsze wyniki w modelach AI LLM, a także 2,5 razy lepsze wyniki w modelach translacyjnych. AMD pokazało także 3,1-krotną przewagę w naukowych obciążeniach NAMD z modelem 128-rdzeniowym oraz prezentację na żywo, w której Turin dostarczał 4 razy więcej tokenów na sekundę niż Xeon.

Zen 5c w centrach danych

Nowe chipy z rdzeniami Zen 5c będą miały do 192 rdzeni i 384 wątków i będą wykonane w procesie 3nm. Ich układ I/O (IOD) będzie natomiast powstawał w technologii 6 nm. Chip składać się będzie łącznie z 17 chipletów. Modele o najwyższej liczbie rdzeni wykorzystują architekturę Zen 5c, która używa rdzeni zoptymalizowanych pod kątem gęstości, a więc o nieco niższych osiągach pojedynczego rdzenia, podobnych do e-cores Intela. 192-rdzeniowe chipy Zen 5c są kontynuacją serii EPYC Bergamo, pierwszych procesorów x86 do centrów danych z rdzeniami zoptymalizowanymi pod kątem gęstości (Zen 4c). Bergamo osiąga maksymalnie 128 rdzeni.

192-rdzeniowe procesory EPYC Turin są zaprojektowane z myślą o najwyższej gęstości rdzeni. Mają zoptymalizowany rdzeń Zen 5c, który zmniejsza powierzchnię potrzebną na każdy rdzeń o połowę, ale obsługuje te same funkcje co pełne rdzenie Zen 5, co czyni je wyjątkowo atrakcyjnymi dla hyperscalerów (AMD twierdzi, że posiada 50% tego segmentu rynku).

Chipów Zen 5c Turin będą konkurować z 144-rdzeniowymi chipami Intel Sierra Forest, które wprowadzają rdzenie Efficiency (E-cores) do linii Xeon dla centrów danych, oraz z 192-rdzeniowymi procesorami AmpereOne, nie wspominając o niestandardowych układach opracowywanych lub stosowanych przez Google i Microsoft.

Zen 5 w centrach danych

Modele z pełnowydajnymi rdzeniami w architekturze Zen 5 będą miały 12 chipletów obliczeniowych wykonanych w procesie N4P i jeden centralny chip IOD wykonany w 6nm, co daje łącznie 13 chipletów. Standardowe modele Turin z architekturą Zen 5 będą miały do 128 rdzeni, co stanowi znaczny postęp w stosunku do obecnej generacji EPYC Genoa, która ma maksymalnie 96 rdzeni.

EPYC Zen 5 będą rywalizować z nadchodzącą serią Xeon 6 Intela. Turin będzie kompatybilny z płytami głównymi używającymi tego samego gniazda SP5, co procesory 4. generacji EPYC Genoa i Bergamo, co umożliwi prostą modernizację do znacznie szybszego chipu. Ta taktyka również przyspiesza kwalifikacje na nowszych płytach głównych i serwerach, umożliwiając szybsze wprowadzenie na rynek.