Indie ogłaszają uniezależnienie się od zewnętrznych producentów procesorów, ponieważ opracowali własny układ obliczeniowy Aum HPC

Obecnie najpotężniejszym procesorem Arm na świecie jest procesor A64FX o 48 rdzeniach firmy Fujitsu, który został stworzony jako silnie wektorowy układ obliczeniowy dla superkomputera “Fugaku” w laboratorium RIKEN w Japonii. Nvidia przygotowuje się do wysyłki swojego procesora Arm “Grace” o 72 rdzeniach, któremu jeszcze nie nadano nazwy produktu, ale logiczne wydaje się oznaczenie CG100. Obaj będą mieć jednak poważną konkurencję ze strony nowego gracza z Indii.

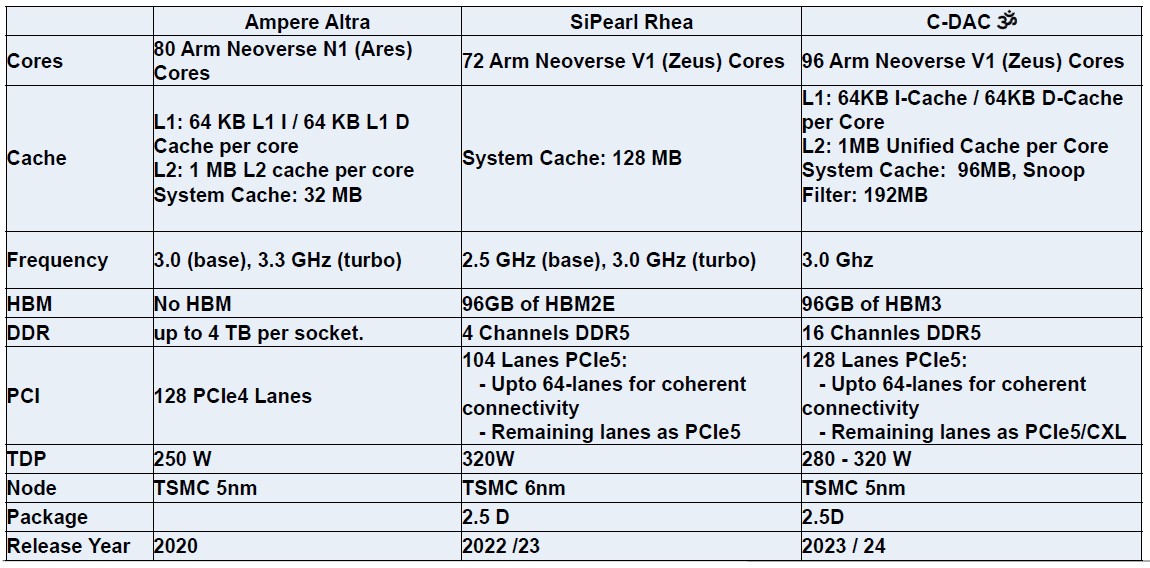

Istnieje pewne prawdopodobieństwo, że procesor HPC Aum zaprojektowany przez Center for Development of Advanced Computing (C-DAC) może przewyższyć zarówno A64FX, jak i Grace, a nawet konkurować z 64-rdzeniowym układem Graviton3 od Amazona oraz procesorami Altra, Altra Max i AmpereOne od Ampere Computing w przypadku bardziej ogólnych obciążeń roboczych.

Szczegóły dotyczące procesora HPC Aum zostały ujawnione w tym tygodniu. Procesor HPC Aum został opracowany w ramach Narodowej Misji Superkomputerowej indyjskiego rządu, a prezentację, którą widzieliśmy, przygotował Sanjay Wandhekar, starszy dyrektor w Grupie Technologii HPC w C-DAC.

Misja ta łączy Indian Institute of Science, Ministerstwo Nauki i Technologii, Ministerstwo Elektroniki i Technologii Informacyjnej oraz C-DAC w celu zapewnienia niezależności HPC, począwszy od procesora, aż po kompleksowe systemy i oprogramowanie, dla rządu Indii i organizacji potrzebujących przetwarzania HPC oraz prawdopodobnie dla indyjskich gigantów przemysłowych, którzy również nie chcą być zależni od zewnętrznych źródeł układów scalonych, systemów i oprogramowania do swoich obciążeń HPC i AI. Jest to nie tylko wysiłek technologiczny, ale także dotyczący produkcji oraz projektowania centrów danych, ze szczególnym naciskiem na chłodzenie cieczą dla najbardziej wydajnych, eksaskalowych maszyn. W ramach tego wysiłku prowadzone jest również rozwijanie aplikacji superkomputerowych “o znaczeniu narodowym” oraz rozwój programowania i uruchamiania tych aplikacji w produkcji.

Ponadto, oprócz stworzenia łańcucha dostaw części i systemów HPC, który byłby odporny na ewentualny import do Indii, indyjskiemu rządowi zależy również na tym, by bez wątpienia wiedzieć, że w sprzęcie lub oprogramowaniu wykorzystywanym do wdrażania aplikacji HPC i AI nie ma żadnych luk bezpieczeństwa. Biorąc pod uwagę, że Indie są potęgą nuklearną, która dzieli granicę z Chinami i znajduje się zaledwie rzut kamieniem od Rosji, nietrudno zrozumieć, dlaczego Indie przyjmują architekturę Arm i wykonują niestandardowy procesor. I nie będzie zaskoczeniem, gdy Pakistan, który również graniczy z Indiami i który ma mniej więcej taką samą liczbę broni jądrowej jak Indie, również wykona niestandardowy procesor. Być może będzie on oparty na RISC-V?

Procesor HPC Aum nie jest ograniczony do rynku HPC, można się spodziewać, że jego warianty będą wykorzystywane również w przestrzeniach związanych z AI i ogólnym przetwarzaniem w chmurze. Oczekuje się, że chip będzie dostępny w 2024 roku i początkowo zostanie wdrożony w pilotażowym systemie HPC o wydajności przekraczającej 1 petaflops (prawdopodobnie jest to teoretyczna wydajność szczytowa). Następnie indyjski rząd zamierza “być gotowy z projektem i podsystemami eksaskalowymi” opartymi na procesorze Aum.

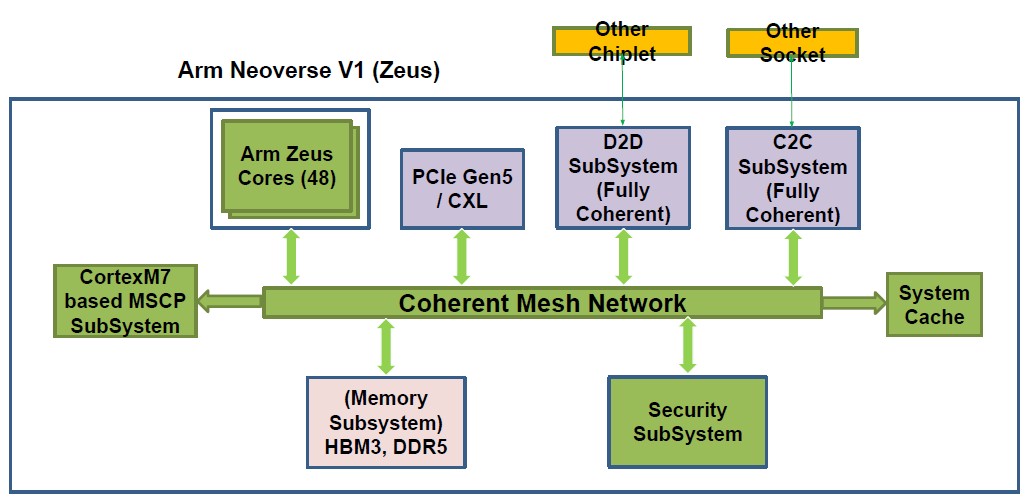

Schemat blokowy procesora AUM

Aby stworzyć procesor Aum, technicy z C-DAC studiowali procesor A64FX i system Fugaku w RIKEN, a także jego poprzednik, procesor Sparc64-VIIIfx, i superkomputer K, i zauważyli to, co wszyscy widzą w danych benchmarkowych HPCG od pierwszego ich udostępnienia. A mianowicie: uzyskanie lepszego stosunku przepustowości pamięci do operacji zmiennoprzecinkowych na sekundę faktycznie wpływa na wydajność aplikacji w rzeczywistości. W rzeczywistości system K ma stosunek bajtów/flops równy 0,5 i osiągnął 5,2% wydajności maksymalnej na teście HPCG, w porównaniu do stosunku bajtów/flops równego 0,38 i wyniku 3% dla Fugaku. (Innymi słowy, wydajność zmniejszyła się przy skoku pokoleniowym w RIKEN.) Dlatego C-DAC postanowiło podnieść stosunek przepustowości pamięci do operacji zmiennoprzecinkowych powyżej 0,5. Ponadto, C-DAC chciało unikać GPU i innych akceleratorów oraz stosować relatywnie małe wektory, które są łatwiejsze do optymalizacji, oraz zapewnić mieszankę pamięci HBM i DDR, oraz dużą liczbę linii wejścia/wyjścia PCI-Express z obsługą CXL.