JEDEC finalizuje standard HBM4 – nowa generacja pamięci dla AI i HPC

JEDEC ogłosiło finalizację specyfikacji HBM4 – nowego standardu pamięci wysokoprzepustowej (High Bandwidth Memory), zaprojektowanego z myślą o rosnących wymaganiach obliczeniowych sztucznej inteligencji, superkomputerów oraz nowoczesnych centrów danych. Oficjalny dokument standardu został opublikowany jako JESD238 i wprowadza istotne zmiany architektoniczne, mające na celu poprawę przepustowości, pojemności i efektywności energetycznej pamięci.

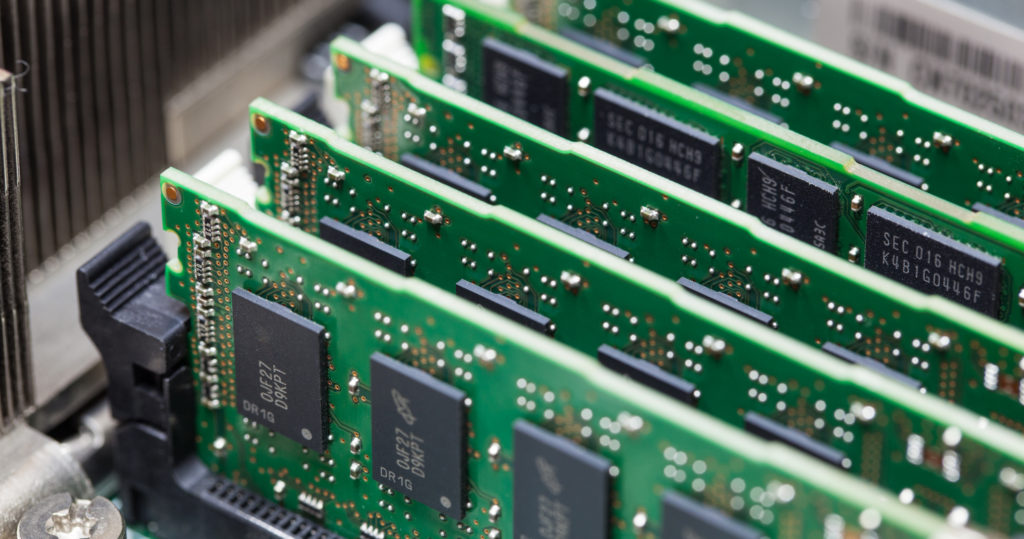

HBM4 kontynuuje ideę pionowego układania warstw DRAM (tzw. „stosów”), która charakteryzuje całą rodzinę HBM, ale znacząco rozwija możliwości swojego poprzednika – HBM3. Nowy standard oferuje transfery z prędkością do 8 Gb/s na interfejsie o szerokości 2048 bitów, co przekłada się na imponującą przepustowość do 2 TB/s. Kluczową nowością jest podwojenie liczby niezależnych kanałów w stosie – z 16 do 32 – z których każdy zawiera dwa pseudo-kanały. Zmiana ta poprawia elastyczność dostępu i zwiększa równoległość operacji pamięciowych.

Nowy standard wprowadza też szeroki zakres napięć zasilających – zarówno dla interfejsów (VDDQ: 0,7–0,9 V), jak i rdzeni (VDDC: 1,0–1,05 V) – co ma przełożyć się na lepszą efektywność energetyczną i możliwość dopasowania do różnych konfiguracji systemowych. Co istotne, HBM4 zachowuje wsteczną kompatybilność z kontrolerami HBM3, co ułatwia migrację do nowego rozwiązania bez konieczności pełnej wymiany infrastruktury.

Standard HBM4 wprowadza także nowe funkcje zwiększające niezawodność i odporność na błędy, takie jak Directed Refresh Management (DRFM), które wspiera ochronę przed efektami typu row-hammer oraz poprawia parametry RAS (Reliability, Availability, Serviceability). W zakresie pojemności, nowe układy mogą zawierać od 4 do 16 warstw DRAM o gęstości 24 Gb lub 32 Gb, co pozwala osiągnąć pojemność do 64 GB w jednym stosie.

Ważną nowością architektoniczną jest również rozdzielenie magistral danych i komend, co pozwala na lepszą równoległość i niższe opóźnienia – szczególnie istotne w scenariuszach obciążeniowych charakterystycznych dla AI i HPC. HBM4 oferuje też nowy interfejs fizyczny oraz ulepszoną integralność sygnału, co ma umożliwić jeszcze wyższe prędkości transmisji danych.

W prace nad HBM4 zaangażowani byli kluczowi gracze branży pamięciowej – Samsung, Micron i SK hynix – którzy już zapowiadają wprowadzenie pierwszych produktów zgodnych z nowym standardem. Samsung planuje rozpoczęcie produkcji HBM4 w 2025 roku, odpowiadając na rosnące potrzeby producentów układów AI i operatorów centrów danych.

Wprowadzenie HBM4 stanowi kolejny krok w ewolucji pamięci zaprojektowanej pod kątem intensywnych obciążeń danych. Nowy standard ma sprostać rosnącym wymaganiom modeli AI i zaawansowanych systemów obliczeniowych, oferując jednocześnie większą wydajność i elastyczność konstrukcyjną.