Kioxia i WD zaprezentują szczegóły dotyczące pamięci 3D NAND z ponad 300 warstwami

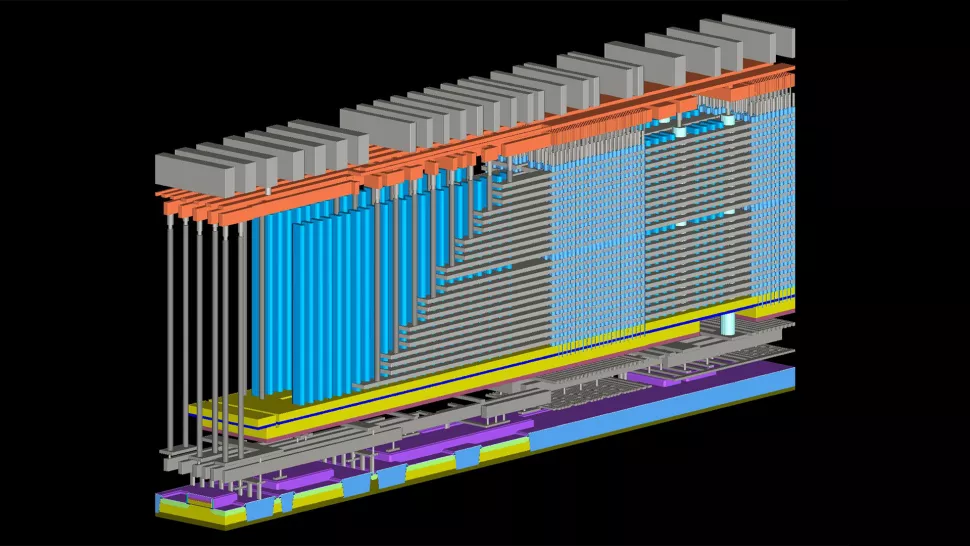

Kioxia oraz jej partner badawczy i produkcyjny Western Digital planują ujawnić swoje innowacje, które pozwolą na uzyskanie większej pojemności i wydajności pamięci 3D NAND na zbliżającym się Sympozjum 2023 dotyczącym technologii i układów VLSI. Inżynierowie z obu firm chcą umożliwić stworzenie 8-płaszczyznowych urządzeń 3D NAND, jak również układów scalonych 3D NAND z ponad 300 liniami słów, donosi eeNewsEurope.

W miarę jak urządzenia 3D NAND zwiększają liczbę linii wyrazowych, zmniejszają wymiary komórek NAND i zwiększają pojemność układów pamięci, kluczowe staje się zwiększenie ich wydajności w zakresie odczytu/zapisu.

Jednym ze sposobów na poprawę wydajności układu scalonego 3D NAND jest zwiększenie liczby płaszczyzn i wzmocnienie jego wewnętrznej równoległości. Kioxia opublikowała referat (C2-1) dotyczący ośmiopłaszczyznowego układu 3D TLC NAND o pojemności 1 TB, posiadającego ponad 210 aktywnych warstw i interfejs o przepustowości 3,2 GT/s. Układ przypomina 218-warstwowe urządzenie 1Tb 3D TLC NAND firmy Kioxia/Western Digital, o gęstości 17Gb/mm^2 i magistrali I/O 3.2 GT/s, zaprezentowany pod koniec marca, jednak posiada on osiem płaszczyzn zamiast czterech i ma oferować 205 MB/s przepustowości oraz opóźnienie odczytu na poziomie 40 μs. Ta ostatnia specyfikacja jest znacznie lepsza niż 56 μs oferowane przez 128-warstwową pamięć 3D NAND firmy Kioxia.

Nowy dokument ujawnia, że 1Tb 3D TLC NAND firmy Kioxia osiągnął prędkość interfejsu 3.2 GT/s poprzez zmniejszenie obszaru zapytań o dane w kierunku X do 41%, co pozwala na szybszy transfer danych pomiędzy pamięcią a hostem. Jednakże ta nowa konstrukcja może prowadzić do przeciążenia połączeń, co Kioxia złagodziła poprzez wprowadzenie hybrydowych dekoderów adresów rzędów (X-DEC). X-DEC pomagają efektywnie zarządzać zwiększoną gęstością połączeń, minimalizując degradację opóźnień odczytu, które mogłyby wynikać z zatorów.

Kioxia zaimplementowała również technikę “jeden impuls-dwa sygnały”, która umożliwia wykrycie dwóch komórek pamięci w jednym impulsie, skracając całkowity czas wykrywania o 18% i zwiększając przepustowość programu do 205 MB/s. Nowatorska ośmiopłaszczyznowa architektura urządzenia, metoda one-pulse-two-strobe oraz 3,2 GT/s I/O pozwalają na uzyskanie opóźnienia odczytu na poziomie 40 μs i przepustowości programu na poziomie 205 MB/s.