Marvell rozwija niestandardową architekturę HBM we współpracy z Micronem, Samsungiem i SK hynix

Marvell ogłosił, że przygotowuje nową niestandardową architekturę obliczeniową HBM, która umożliwia jednostkom XPU osiągnięcie większej gęstości obliczeniowej i pamięci. Zgodnie z komunikatem prasowym ta nowa architektura akceleratora AI (XPU) umożliwia do 25% więcej obliczeń, 33% więcej pamięci przy jednoczesnej poprawie efektywności energetycznej.

Co ciekawe, nowa niestandardowa architektura XPU firmy Marvell została opracowana we współpracy z wiodącymi producentami pamięci, czyli Micronom, Samsungiem i SK hynix, jak wskazuje komunikat prasowy.

Nowy produkt ma zapewnić specjalistyczne interfejsy zaprojektowane specjalnie dla operatorów centrów danych w chmurze. Zgodnie z komunikatem prasowym architektura umożliwia wydajniejsze skalowanie jednostek XPU, pomagając dostawcom chmury budować solidną infrastrukturę dla rosnących wymagań sztucznej inteligencji.

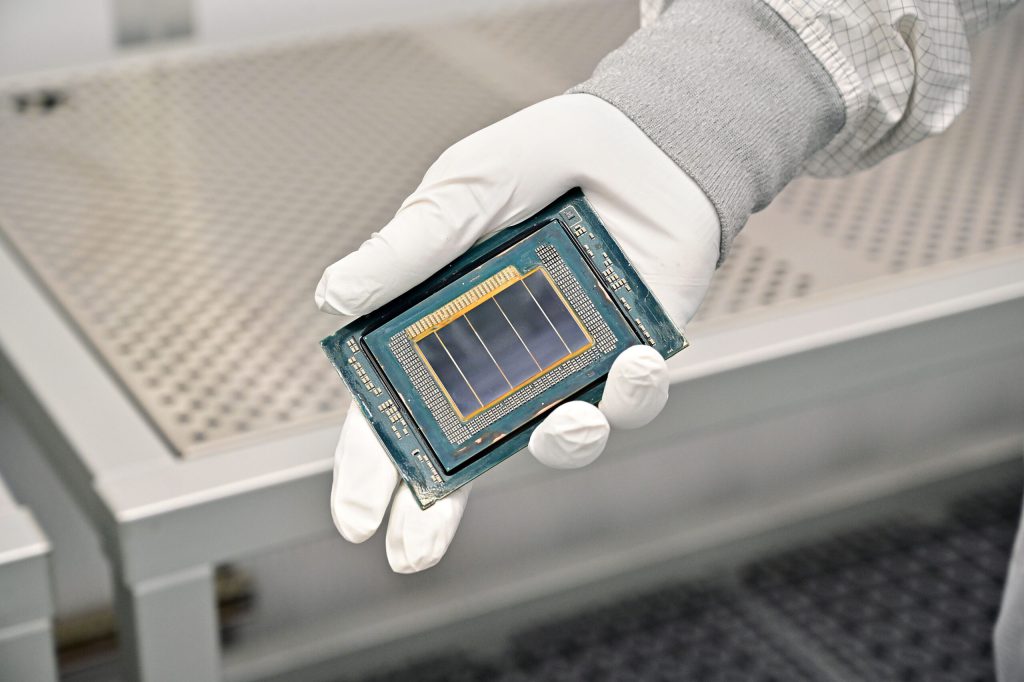

Komunikat prasowy wskazuje, że wspomniana architektura obliczeniowa poprawia wydajność XPU dzięki innowacyjnej konstrukcji interfejsu. Z kolei dzięki serializacji i przyspieszeniu interfejsów I/O między krzemowymi układami scalonymi akceleratora obliczeniowego AI a podstawowymi układami HBM architektura ta zmniejsza zużycie energii nawet o 70% w porównaniu ze standardowymi interfejsami HBM. Co więcej, ta konstrukcja interfejsu zmniejsza wymaganą powierzchnię krzemową w każdym układzie scalonym, umożliwiając integrację logiki obsługi HBM z podstawowym układem scalonym.

W materiale wskazano, że te oszczędności powierzchni do 25% pozwalają na zwiększenie możliwości obliczeniowych poprzez obsługę do 33% więcej stosów HBM, co znacznie zwiększa pojemność pamięci na jednostkę XPU.