Optyczne połączenie PCIe 7.0 osiąga niesamowitą prędkość 128 GT/s

Firma Cadence zademonstrowała swoje autorskie rozwiązanie łączności optycznej dla PCIe 7.0 podczas PCI-SIG DevCon 2024 na początku tego miesiąca.

Pierwsza na świecie demonstracja połączenia 128 GT/s PCIe 7.0 za pośrednictwem optyki jest nadal w dużej mierze koncepcją, ponieważ specyfikacja PCIe 7.0 nie została jeszcze sfinalizowana. Jednak posiadanie działającego rozwiązania łączności optycznej dla standardu, który ma być używany pod koniec dekady, wyraźnie pokazuje techniczną sprawność Cadence.

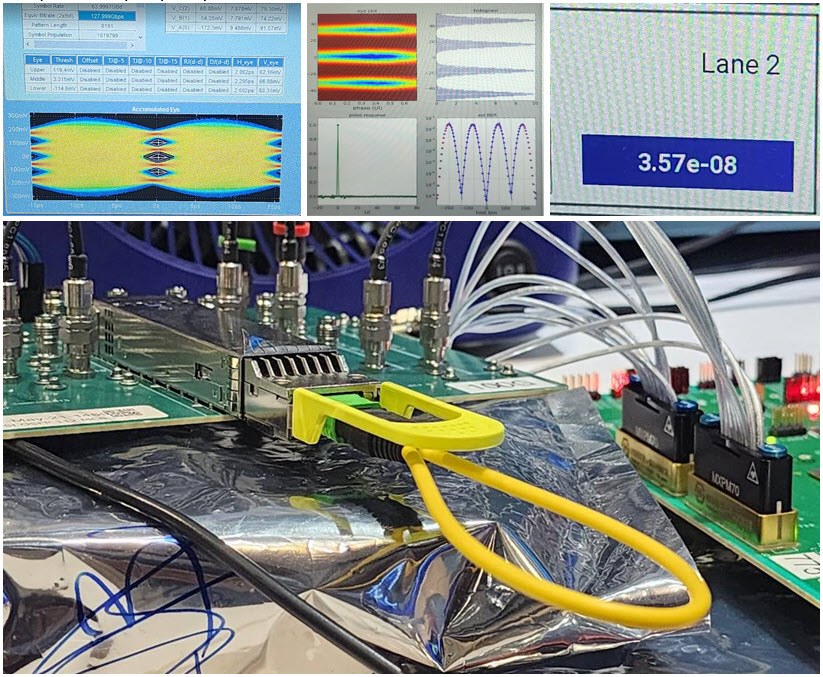

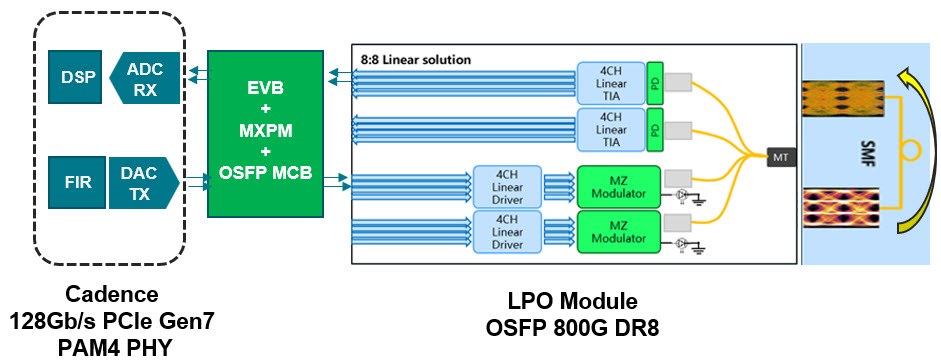

Podczas wydarzenia firma zademonstrowała możliwości transmisji i odbioru 128 GT/s PCIe 7.0 IP przy użyciu rzeczywistego, liniowego połączenia optycznego o niskim opóźnieniu, bez retimingu. Konfiguracja ta konsekwentnie osiągała współczynnik BER pre-FEC na poziomie ~3E-8, znacznie poniżej wymogu specyfikacji PCIe wynoszącego 1E-6, co czyni ją pierwszą stabilną demonstracją 128 GT/s przez standardowe złącza optyczne. Histogramy odbiornika Eye PAM4, przedstawione na obrazie zademonstrowanym przez Cadence, wykazują doskonałą liniowość i margines.

W sierpniu ubiegłego roku PCI-SIG utworzyło Optical Workgroup, która będzie pracować nad przemysłowym standardem PCIe dla interfejsów optycznych. Do tej pory PCI Express opierało się wyłącznie na połączeniach miedzianych.

Połączenia PCIe stają się coraz dłuższe w zastosowaniach takich jak serwery AI i HPC, a użycie retimerów jest zarówno skomplikowane, kosztowne i energochłonne, jak i ma swoje ograniczenia (ponieważ można użyć tylko dwóch retimerów na łącze). Dlatego decyzja o zbadaniu łączności optycznej jest z pewnością ważna.

Podobnie jak Cadence, kilku innych dostawców oferuje obecnie własne rozwiązania w zakresie zewnętrznej łączności PCIe. Nie musi to być sprzeczne z planem PCI-SIG dotyczącym standaryzacji optycznej łączności PCIe, ponieważ opracowanie standardu optycznego ma na celu ustanowienie ujednoliconego podejścia do PCIe przez światłowody. PCI-SIG podkreśliło, że nie tworzy standardu dla żadnej konkretnej technologii optycznej, ale ma na celu opracowanie specyfikacji niezależnej od technologii, która obsługuje szerokie spektrum technologii optycznych.

Rozwiązanie optyczne dla PCIe 7.0 będzie wymagane w nadchodzących latach. Firma Cadence zaprezentowała jednak podczas wydarzenia sporo konfiguracji PCIe, w tym elektryczne PCIe 7.0 i różne konfiguracje PCIe 6.0. Obejmowały one konfiguracje RP/EP interop back-to-back, demonstracje protokołów w trybie FLIT zarówno na stoiskach Cadence, jak i Lecroy, testy JTOL przy użyciu sprzętu Anritsu i Tektronix oraz demonstracje interoperacyjności na poziomie systemu z platformą PCIe Gen5 na stoisku SerialTek.