Rozwiązanie 3D DRAM otwiera drogę do zwiększenia gęstości pamięci

Jeśli istnieje jeden produkt technologiczny, gdzie skalowanie nie działa tak dobrze, to jest to pamięć DRAM. Istnieje ku temu wiele powodów, z których najważniejszym jest faktyczny projekt komórek DRAM i ich związek z produkcją. Jednak według Lam Research, końcowy rezultat tych trudności ze skalowaniem oznacza, że naukowcy w dziedzinie DRAM mogą nie mieć możliwości zwiększenia skalowania gęstości DRAM już za pięć lat.

W tym kontekście Lam Research, firma specjalizująca się w projektowaniu obwodów półprzewodnikowych, opublikowała propozycję ewolucji przyszłych produktów DRAM. Przyszłością może być 3D, więc wydaje się, że sześciany pamięci nie są tak daleko poza sferą możliwości. Według firmy, zaprojektowanie nadającego się do produkcji urządzenia 3D DRAM zajmie nam około pięciu do ośmiu lat, pozostawiając światu możliwą trzyletnią lukę między momentem zakończenia skalowania 2D DRAM a wzrostem skalowania 3D DRAM.

Korzystając z własnego oprogramowania SEMulator3D, firma Lam Research przeprowadziła iterację możliwych projektów 3D DRAM. Skupiono się na rozwiązaniu wyzwań związanych ze skalowaniem i układaniem warstw, zmniejszaniem kondensatorów i tranzystorów, łącznością między komórkami i układami przelotek (takimi jak TSV [Through Silicon Vias] firmy TSMC, które widzieliśmy już w innych projektach półprzewodników 3D). Wreszcie, firma określiła wymagania procesowe, które umożliwiają produkcję proponowanego przez nią projektu.

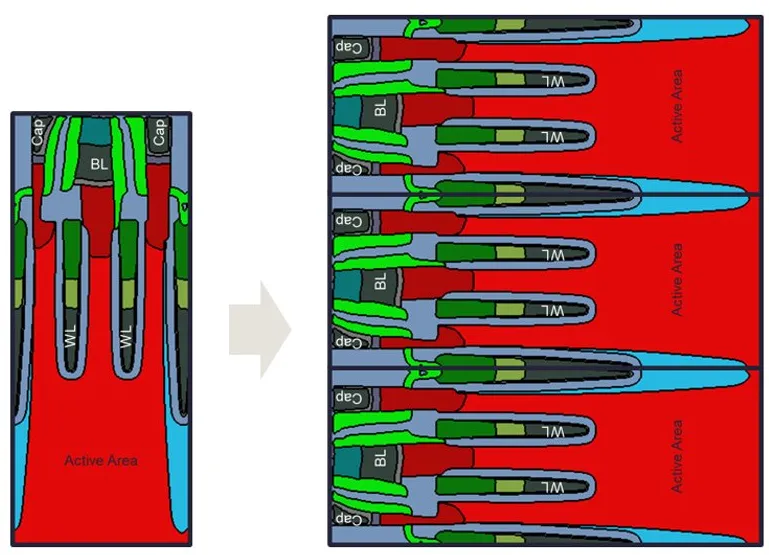

Widok architektury 2D DRAM zorientowanej pionowo (po lewej), taki sam projekt stosowany w obecnych architekturach DRAM. Odwrócenie jej i ułożenie struktur jedna na drugiej (po prawej) jest niepraktyczne głównie ze względu na konieczność wytrawiania i wypełniania bocznych wnęk o różnej głębokości w aktywnym obszarze krzemu. (Źródło zdjęcia: Lam Research)

Ze względu na sposób, w jaki projektowane są komórki DRAM, nie będzie można po prostu położyć komponentów 2D DRAM na boku, aby następnie ułożyć je jeden na drugim. Dzieje się tak, ponieważ komórki DRAM mają wysoki współczynnik proporcji (są wyższe niż grube). Ułożenie ich na boku wymagałoby bocznego wytrawiania (i wypełniania), które wykracza poza nasze obecne możliwości.

Kiedy jednak zrozumie się samą architekturę, można ją zmieniać i dostosowywać, próbując jednocześnie ominąć ograniczenia projektowe. Łatwiej to jednak powiedzieć niż zrobić i jest powód, dla którego nie mamy jeszcze 3D DRAM.

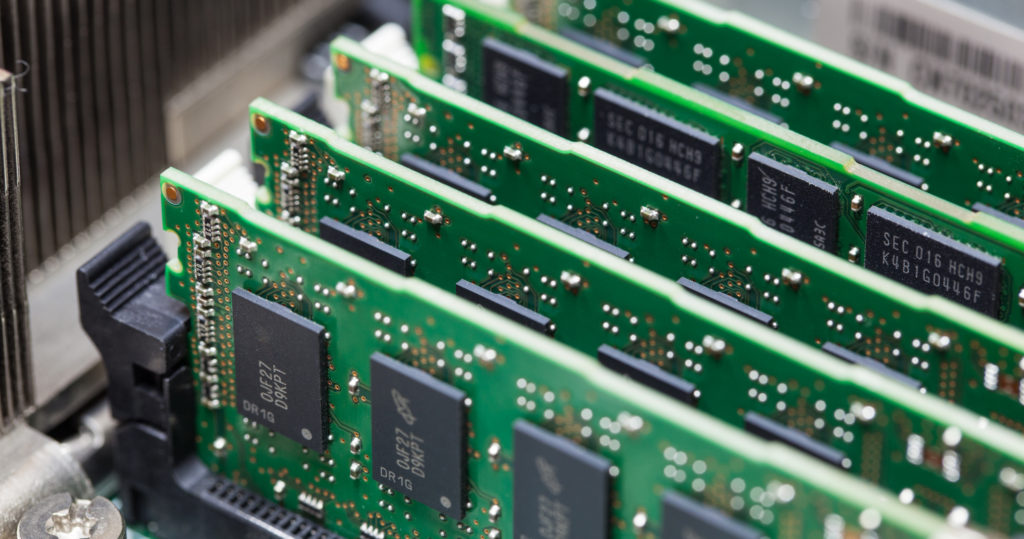

Obecne projekty obwodów DRAM wymagają zasadniczo trzech komponentów: linii bitowej (struktury przewodzącej, która wprowadza prąd); tranzystora, który odbiera prąd wyjściowy linii bitowej i służy jako bramka kontrolująca, od której zależy, czy prąd elektryczny może wpływać do obwodu (i go wypełniać); oraz kondensatora, w którym prąd przepływający przez linię bitową i tranzystor jest ostatecznie przechowywany w postaci bitu (0 lub 1).

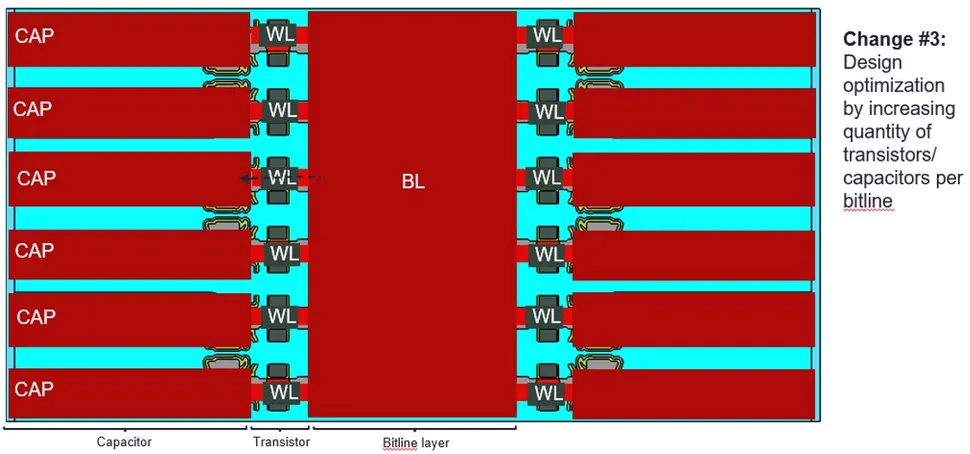

Firma Lam Research wykorzystała kilka “sztuczek” przy projektowaniu układów scalonych, aby osiągnąć działającą architekturę. Po pierwsze, przeniesiono linię bitową na przeciwną stronę tranzystora; ponieważ linia bitowa nie jest już otoczona kondensatorem, oznacza to, że więcej tranzystorów można podłączyć do samej linii bitowej, poprawiając gęstość układu.

Aby zmaksymalizować wzrost gęstości powierzchni, Lam Research zastosował również kilka najnowocześniejszych technik produkcji tranzystorów. Obejmują one projekty forksheetów Gate-All-Around (GAA), które Intel wydaje się badać pod kątem technologii bramek nowej generacji. Przeprojektowana architektura DRAM zaproponowana przez Lam Research może być następnie układana w stosy, z warstwami nowego projektu komórek DRAM jedna na drugiej w procesie podobnym do tego z NAND.

Ostateczny projekt komórki DRAM od Lam Research pozwala na większą liczbę tranzystorów zasilanych przez tę samą linię bitową, poprawiając gęstość pamięci, jednocześnie “spłaszczając” projekt, dzięki czemu jest bardziej odpowiedni do skalowania 3D. (Źródło zdjęcia: Lam Research)

Ale podczas gdy skalowanie NAND wynosi obecnie około 232 warstw, Lam Research szacuje, że pierwsza generacja projektu 3D DRAM, takiego jak jego własny, wykorzystałaby tylko do 28 ułożonych warstw. Dzięki ulepszeniom architektury i dodatkowym warstwom, Lam Research szacuje, że można osiągnąć poprawę gęstości pamięci DRAM o dwa węzły – z dalszymi ulepszeniami możliwymi dzięki dodaniu dodatkowych warstw do stosu DRAM. Jak widzieliśmy w innych technologiach produkcyjnych, wykorzystanie macierzy przelotek (technologia leżąca u podstaw TSMC TSV) jest następnie wykorzystywane do łączenia poszczególnych warstw.

Istnieje jednak bezpośredni problem z projektem zaproponowanym przez Lam Research: Nie ma obecnie narzędzi produkcyjnych, które mogłyby niezawodnie wytwarzać potrzebne funkcje. Firma szybko zauważa, że samo projektowanie pamięci DRAM znajduje się obecnie na krawędzi; ulepszanie i przeprojektowywanie narzędzi i procesów jest powszechnym wymogiem. I jak mówi firma, wciąż mamy czas, zanim zderzymy się ze ścianą skalowania DRAM. Miejmy nadzieję, że wymagane narzędzia i wiedza specjalistyczna pojawią się w tym czasie.