TSMC anonsuje technologię 1,6 nm. Produkcja ma ruszyć za dwa lata

Podczas organizowanego przez firmę Sympozjum Technologicznego Ameryki Północnej w 2024 r. TSMC zaprezentowało dziś swój najnowszy proces wytwarzania półprzewodników, zaawansowane opakowania i technologie 3D IC umożliwiające napędzanie nowej generacji innowacji w zakresie sztucznej inteligencji.

Firma TSMC zadebiutowała technologią TSMC A16TM, obejmującą wiodące tranzystory nanoarkuszowe z innowacyjnym rozwiązaniem tylnej szyny zasilającej, która ma wejść do produkcji w 2026 r., zapewniając znacznie lepszą gęstość logiczną i wydajność.

TSMC wprowadziło także technologię System-on-Wafer (TSMC-SoW™), innowacyjne rozwiązanie, które zapewnia rewolucyjną wydajność na poziomie płytek, spełniając przyszłe wymagania sztucznej inteligencji dla hiperskalerowych centrów danych.

„Wkraczamy w świat oparty na sztucznej inteligencji, w którym sztuczna inteligencja działa nie tylko w centrach danych, ale także w komputerach stacjonarnych, urządzeniach mobilnych, samochodach, a nawet w Internecie rzeczy – powiedział dyrektor generalny TSMC, dr C.C. Wei. – W TSMC oferujemy naszym klientom najbardziej kompleksowy zestaw technologii umożliwiających realizację ich wizji sztucznej inteligencji, od najbardziej zaawansowanego krzemu na świecie, przez najszersze portfolio zaawansowanych opakowań i platform 3D IC, po specjalistyczne technologie integrujące świat cyfrowy z realny świat”.

Technologia TSMC A16TM

Wiodąca w branży technologia N3E firmy TSMC jest już w fazie produkcji, a produkcja N2 ma rozpocząć się w drugiej połowie 2025 r., TSMC zaprezentowało A16, kolejną technologię w swoim planie działania.

A16 połączy architekturę Super Power Rail firmy TSMC z tranzystorami nanoarkuszowymi na potrzeby produkcji planowanej na 2026 rok. Poprawia gęstość logiczną i wydajność, przeznaczając zasoby routingu po stronie frontowej na sygnały, dzięki czemu A16 idealnie nadaje się do produktów HPC ze złożonymi trasami sygnałowymi i gęstymi sieciami zasilania.

W porównaniu z procesem N2P firmy TSMC, A16 zapewni 8–10% poprawę prędkości przy tym samym Vdd (dodatnie napięcie zasilania), 15–20% redukcję mocy przy tej samej prędkości i aż do 1,10-krotną poprawę gęstości chipów w przypadku produktów dla centrów danych.

Innowacja TSMC NanoFlexTM dla tranzystorów nanoarkuszowych

Nadchodząca technologia N2 firmy TSMC będzie dostępna wraz z TSMC NanoFlex, kolejnym przełomem firmy we wspólnej optymalizacji projektowania i technologii.

TSMC NanoFlex zapewnia projektantom elastyczność w zakresie standardowych ogniw N2, podstawowych elementów składowych konstrukcji chipów, z krótkimi ogniwami podkreślającymi mały obszar i większą wydajnością energetyczną oraz wysokimi ogniwami maksymalizującymi wydajność. Klienci mogą zoptymalizować kombinację krótkich i wysokich ogniw w tym samym bloku projektowym, dostosowując swoje projekty, aby osiągnąć optymalne kompromisy w zakresie mocy, wydajności i powierzchni dla ich zastosowania.

Technologia N4C

Wprowadzając zaawansowaną technologię TSMC do szerszego zakresu zastosowań, TSMC ogłosiło N4C, rozszerzenie technologii N4P oferujące redukcję kosztów matrycy do 8,5% i niewielkie nakłady na wdrożenie, którego produkcję masową zaplanowano na 2025 rok.

N4C oferuje wydajne pod względem powierzchni podstawy własności intelektualnej i zasady projektowania, które są w pełni kompatybilne z powszechnie przyjętym N4P, z lepszą wydajnością wynikającą ze zmniejszenia rozmiaru matrycy, zapewniając opłacalną opcję migracji produktów o większej wartości do następnego węzła zaawansowanej technologii firmy TSMC.

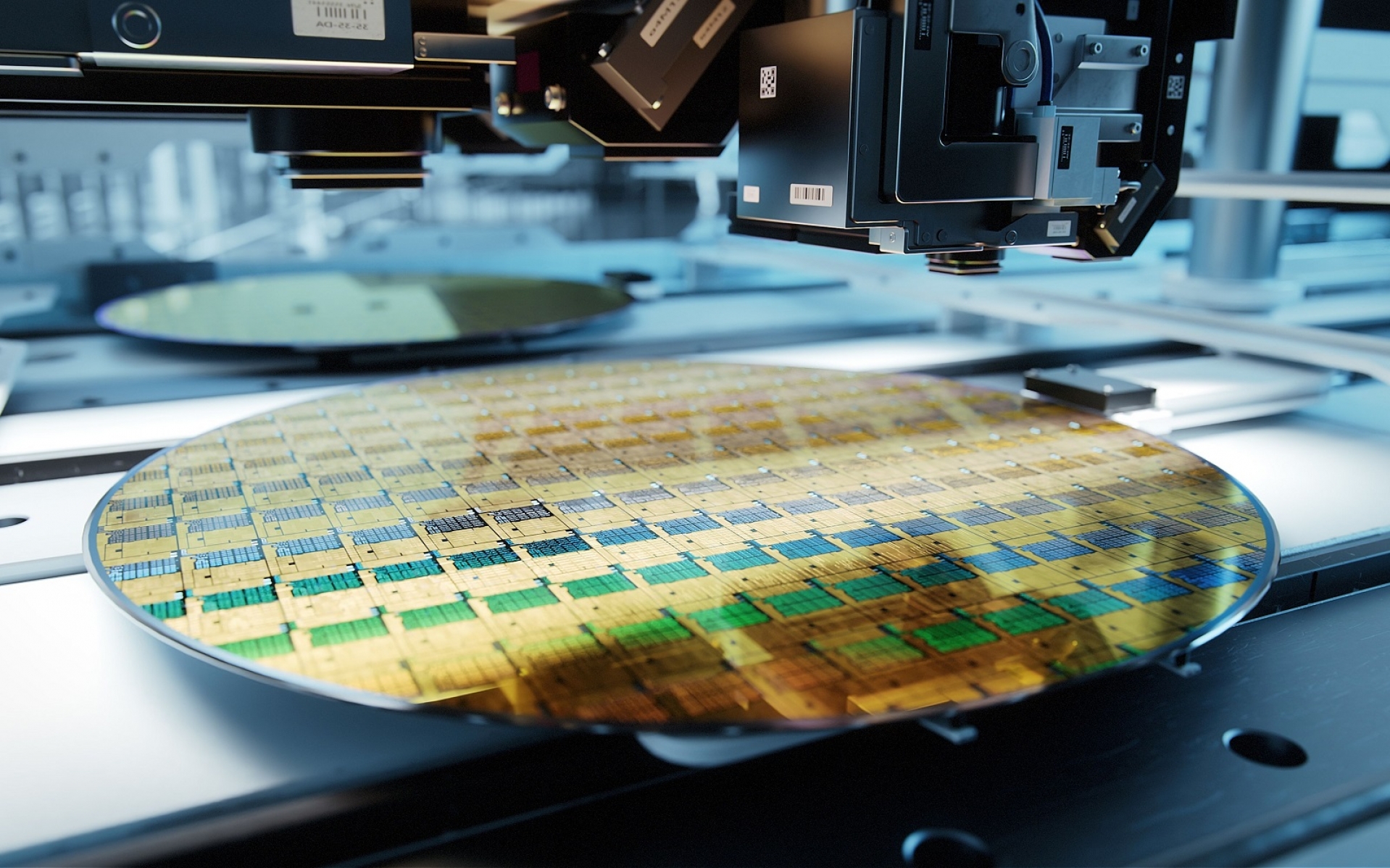

CoWoS, SoIC i System-on-Wafer (SoW)

Chip on Wafer on Substrate (CoWoS) firmy TSMC odegrał kluczową rolę w rewolucji AI, umożliwiając klientom pakowanie większej liczby rdzeni procesorów i stosów pamięci o dużej przepustowości (HBM) obok siebie na jednej przekładce. Jednocześnie System na zintegrowanych chipach (SoIC) stał się wiodącym rozwiązaniem do układania w stosy chipów 3D, a klienci coraz częściej łączą CoWoS z SoIC i innymi komponentami w celu uzyskania najwyższej integracji systemu w pakiecie (SiP).

Dzięki System-on-Wafer firma TSMC zapewnia nową, rewolucyjną opcję umożliwiającą zastosowanie dużej liczby matryc na płytce o średnicy 300 mm, oferując większą moc obliczeniową, zajmując jednocześnie znacznie mniej miejsca w centrum danych i zwiększając wydajność na wat o rzędy wielkości.

Pierwsza oferta SoW firmy TSMC, płytka oparta wyłącznie na logice, oparta na technologii Integrated Fan-Out (InFO), jest już w produkcji. Wersja chip-on-wafer, wykorzystująca technologię CoWoS, ma być gotowa w 2027 r., umożliwiając integrację SoIC, HBM i innych komponentów w celu stworzenia potężnego systemu na poziomie płytki o mocy obliczeniowej porównywalnej z szafą serwerową w centrum danych lub nawet całym serwer.

Integracja z fotoniką krzemową

TSMC opracowuje technologię Compact Universal Photonic Engine (COUPE), aby wspierać gwałtowny wzrost transmisji danych, który towarzyszy boomowi sztucznej inteligencji. COUPE wykorzystuje technologię układania chipów SoIC-X do układania matrycy elektrycznej na matrycy fotonicznej, oferując najniższą impedancję na styku matrycy i wyższą efektywność energetyczną w porównaniu z konwencjonalnymi metodami układania w stosy.

TSMC planuje zakwalifikować COUPE do wtyczek Small Form Factor w 2025 r., a następnie zintegrować je z opakowaniami CoWoS jako optyki pakowane w pakiecie (CPO) w 2026 r., wprowadzając połączenia optyczne bezpośrednio do opakowania.

Automotive Advanced Packaging

Po wprowadzeniu w 2023 roku procesu N3AE „Auto Early”, TSMC w dalszym ciągu zaspokaja potrzeby naszych klientów z branży motoryzacyjnej w zakresie większej mocy obliczeniowej, która spełnia wymagania bezpieczeństwa i jakości na autostradach, poprzez integrację zaawansowanego krzemu z zaawansowanym opakowaniem.

TSMC opracowuje rozwiązania InFO-oS i CoWoS-R do zastosowań takich jak zaawansowane systemy wspomagania kierowcy (ADAS), sterowanie pojazdem i centralne komputery pojazdu, których celem jest uzyskanie kwalifikacji AEC-Q100 Grade 2 do czwartego kwartału 2025 r.