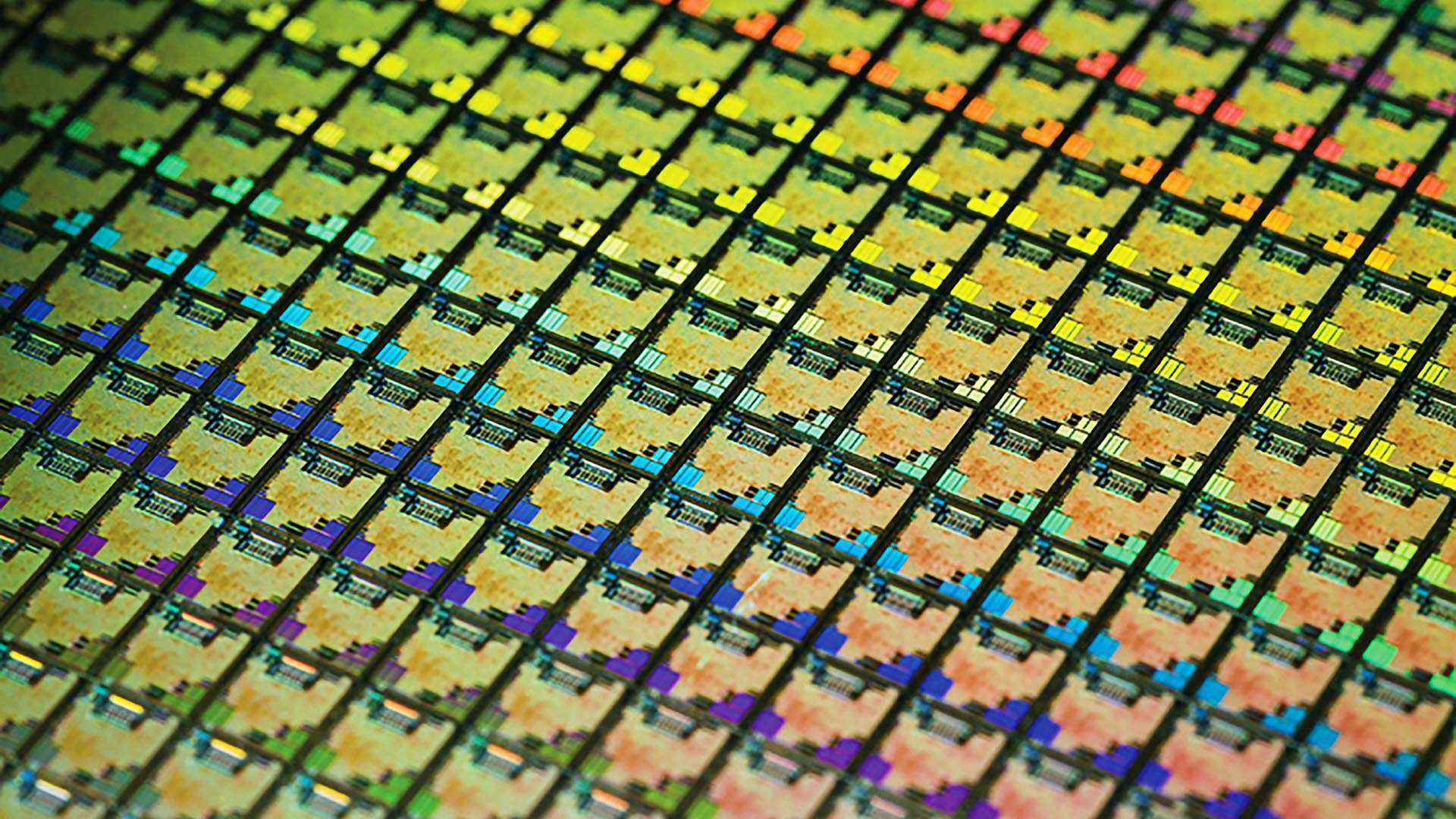

TSMC ma coraz ambitnniejsze plany w zakresie zwiększania wydajności CoWoS

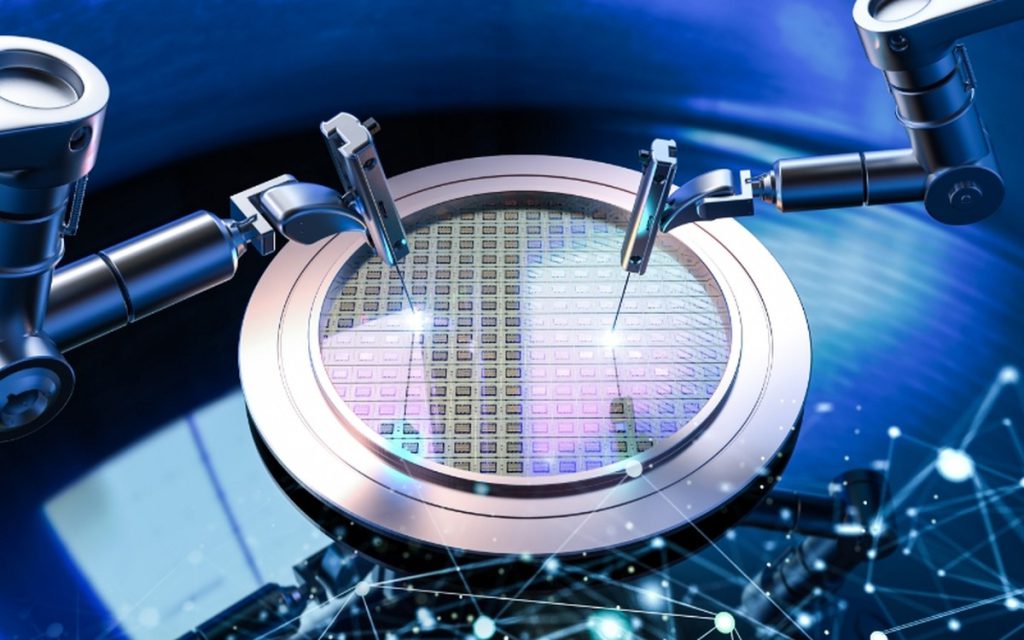

Zapotrzebowanie na procesory AI i HPC stale rośnie, napędzając wykorzystanie zaawansowanych technologii pakowania. TSMC ujawniło plany dalszego zwiększania swojej wydajności w zakresie chip-on-wafer-on-substrate (CoWoS) przy złożonej rocznej stopie procentowej (CAGR) wynoszącej ponad 60% do 2026 roku.

Jak podaje AnandTech, zgodnie z najnowszym planem działania przedstawionym wcześniej na Europejskim Sympozjum Technologicznym firmy, TSMC będzie teraz w stanie do końca 2026 r. ponad czterokrotnie zwiększyć swoją wydajność CoWoS w porównaniu z poziomem z 2023 r. do końca 2026 r.

W zeszłym roku lider produkcji ogłosił plany ponad dwukrotnego zwiększenia wydajności CoWoS do końca 2024 r., ale teraz musi przyjąć ambitniejsze cele, nie tylko by zaspokoić istniejący popyt, ale także zająć się przyszłym rynkiem.

TSMC przygotowuje również dodatkowe wersje CoWoS (w szczególności CoWoS-L) do obsługi budowania systemów w pakietach (SiP) z maksymalnie ośmioma rozmiarami siatki, na wypadek, gdyby czterokrotne zwiększenie wydajności CoWoS w ciągu trzech lat mogło nadal być niewystarczające, zasugerowano w raporcie.

Oprócz CoWoS TSMC planuje również rozszerzyć pojemność układów SoIC (system-on-integrated chip) do roku 2026 przy CAGR wynoszącym 100%, co wskazuje, że do końca 2026 r. pojemność SoIC wzrośnie ośmiokrotnie w porównaniu z poziomem z 2023 roku.

Jeśli chodzi o najnowsze plany ekspansji zagranicznej dotyczące głównych tajwańskich fabryk, w lutym zainaugurowano należącą do TSMC Kumamoto Fab 1, wspólną inwestycję pomiędzy TSMC, Sony Semiconductor Solutions Corporation i Denso Corporation.

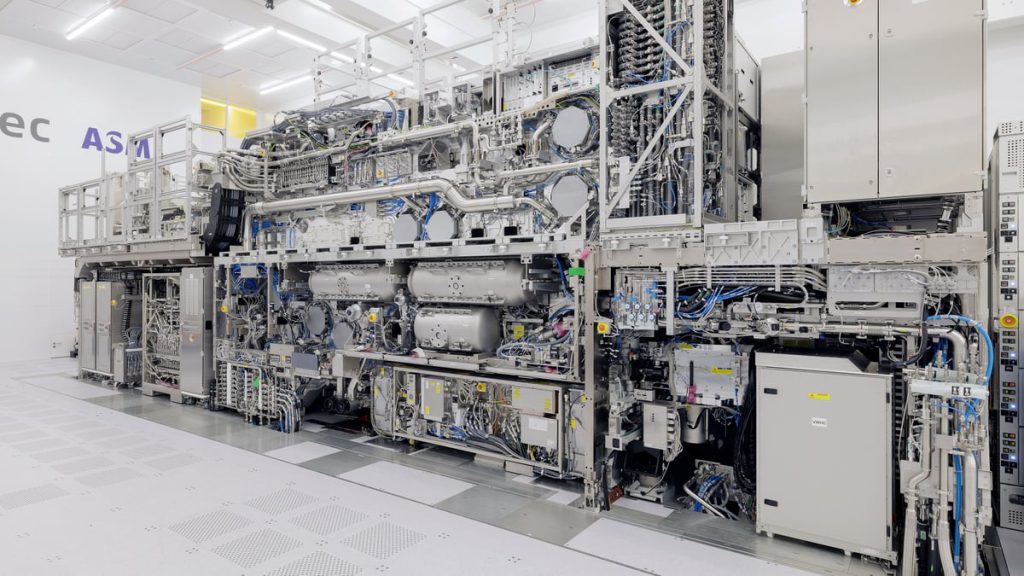

Budowa drugiej fabryki w Kumamoto ma się rozpocząć pod koniec 2024 r., a działalność operacyjna rozpocznie się pod koniec 2027 r. 21 maja UMC, druga co do wielkości odlewnia płytek na Tajwanie, ogłosiła przybycie pierwszych narzędzi sprzętowych do fazy 3 rozbudowy fabryki Fab12i w Singapurze.