TSMC prezentuje mapę drogową na najbliższe lata. Większe i wydajniejsze chipy dla AI

TSMC przedstawiło właśnie ambitną mapę drogową rozwoju technologii pakowania chipów. Firma chce tworzyć coraz większe i bardziej złożone układy, które sprostają wymaganiom sztucznej inteligencji i nowoczesnych centrów danych.

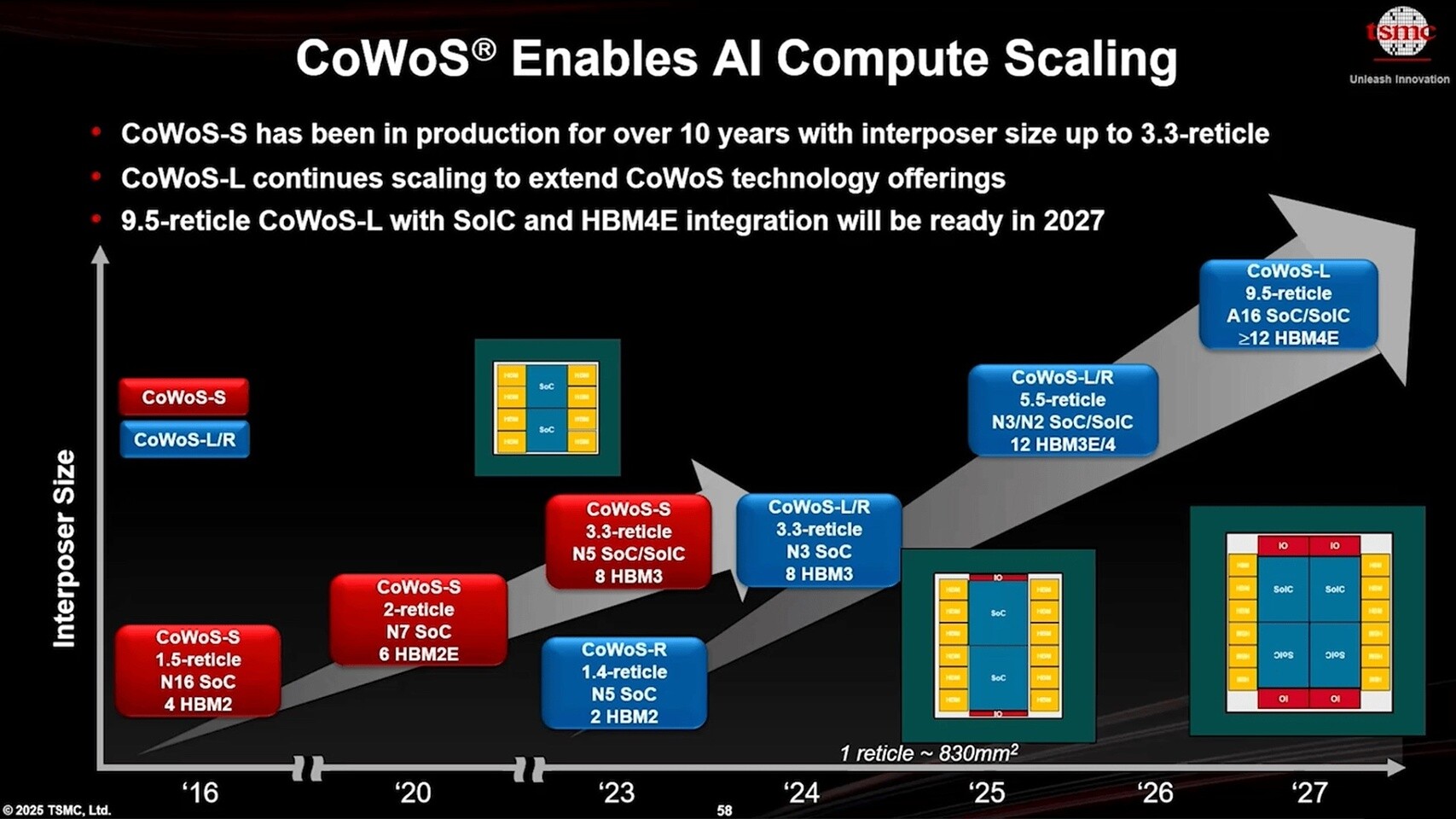

Jeszcze niedawno standardem było łączenie czterech stosów pamięci HBM z procesorem. Dziś TSMC oferuje już układy z ośmioma takimi stosami, a na horyzoncie – w 2027 roku – pojawią się rozwiązania pozwalające na integrację nawet dwunastu stosów HBM3E lub HBM4 oraz wielu zaawansowanych chipletów.

Kluczowe w tej strategii są nowe technologie, takie jak CoWoS-L i System-on-Wafer. CoWoS-L to nowoczesny sposób łączenia różnych elementów, na przykład procesora i pamięci, w jeden wydajny moduł. Wykorzystuje specjalne „mostki” z krzemu (LSI) do szybkiego przesyłania danych między chipami oraz cienkie warstwy przewodzące (RDL) odpowiedzialne m.in. za zasilanie.

System-on-Wafer to jeszcze bardziej zaawansowana technologia, która pozwala łączyć wiele chipów na całej powierzchni wafla, co daje jeszcze większą moc obliczeniową i oszczędność miejsca. Dzięki tym rozwiązaniom można tworzyć układy idealne do zastosowań takich jak AI czy superkomputery.

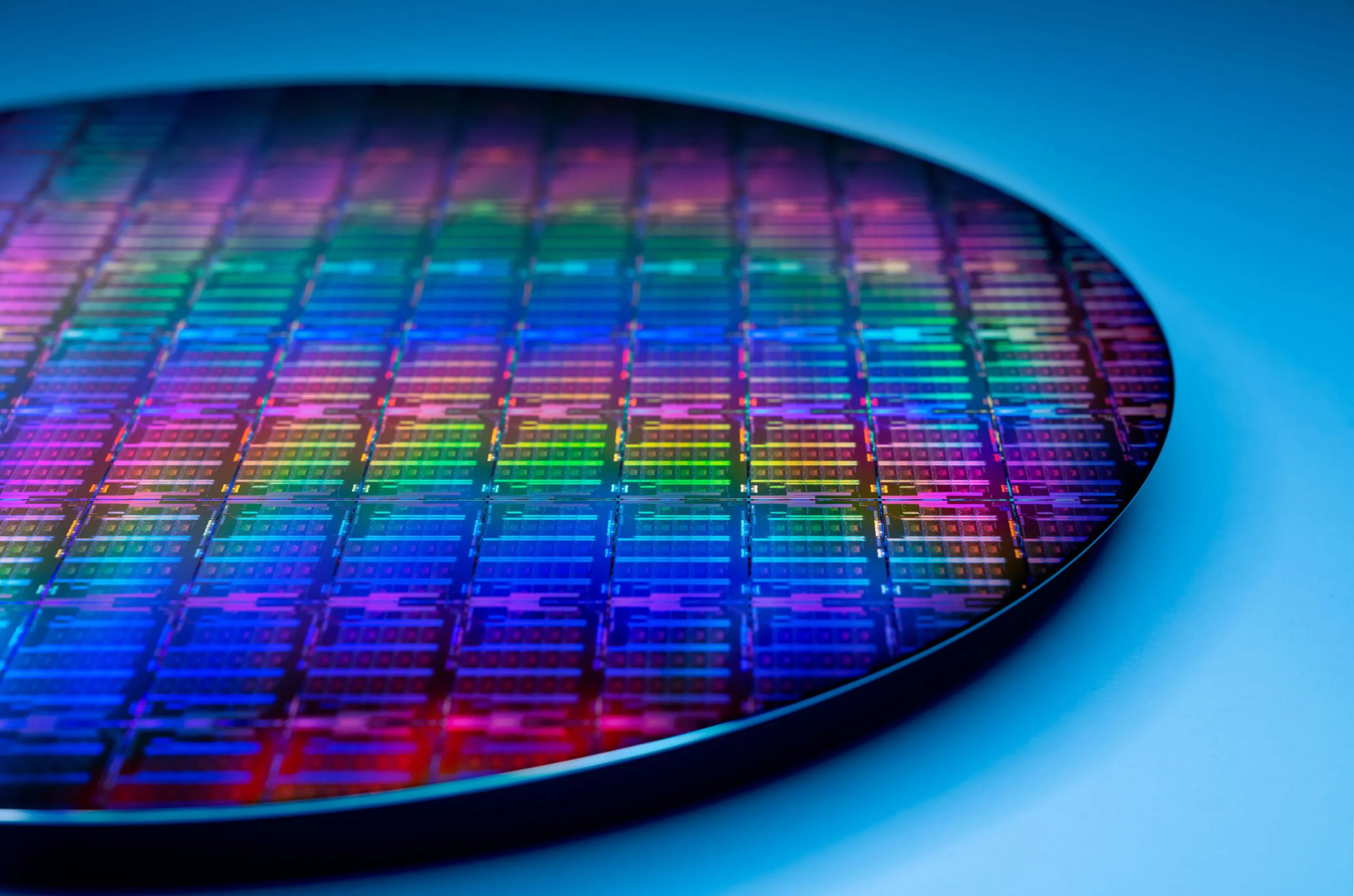

TSMC pracuje też nad przejściem z tradycyjnych okrągłych wafli 12-calowych (304,8 mm średnicy) na prostokątne podłoża o wymiarach 510 x 515 mm. Takie rozwiązanie umożliwi produkcję jeszcze większych i wydajniejszych chipów AI, ograniczając straty materiałowe i poprawiając efektywność pakowania. Nowe podłoża pozwolą na integrację większej liczby chipów i pamięci HBM, co jest kluczowe dla zastosowań w AI i HPC (High Performance Computing).

Przykłady praktycznego zastosowania tych technologii już dziś można znaleźć w kartach AMD Instinct czy NVIDIA Rubin, a linie produkcyjne TSMC są zarezerwowane przez największych graczy branży AI aż do końca 2025 roku. Pierwsze układy nowej generacji mają trafić na rynek już w 2026 roku, a pełne wdrożenie najbardziej zaawansowanych rozwiązań nastąpi w 2027.