TSMC prezentuje proces produkcyjny 3 nm, i wyzwania z nim związane

Według raportu WikiChip, skalowanie pamięci SRAM przez TSMC uległo znacznemu spowolnieniu. Jeśli chodzi o nowe węzły produkcyjne, oczekujemy, że zwiększą one wydajność, zmniejszą zużycie energii i zwiększą gęstość tranzystorów.

Jednak podczas gdy układy logiczne dobrze się skalują dzięki ostatnim technologiom procesowym, komórki SRAM pozostają w tyle i najwyraźniej prawie przestały się skalować w węzłach produkcyjnych TSMC klasy 3 nm. Jest to poważny problem dla przyszłych procesorów, układów graficznych i SoC, które będą prawdopodobnie coraz droższe z powodu wolnego skalowania się powierzchni komórek SRAM.

Kiedy TSMC formalnie zaprezentowało swoje technologie produkcyjne N3 na początku tego roku, powiedziało, że nowe węzły zapewnią 1,6x i 1,7x poprawę gęstości logicznej w porównaniu do procesu N5. To, czego nie ujawniła wtedy firma, to fakt, że komórki SRAM w nowych technologiach prawie nie skalują się w porównaniu do N5, jak podaje WikiChip, która uzyskała informacje z dokumentu TSMC opublikowanego na International Electron Devices Meeting (IEDM)

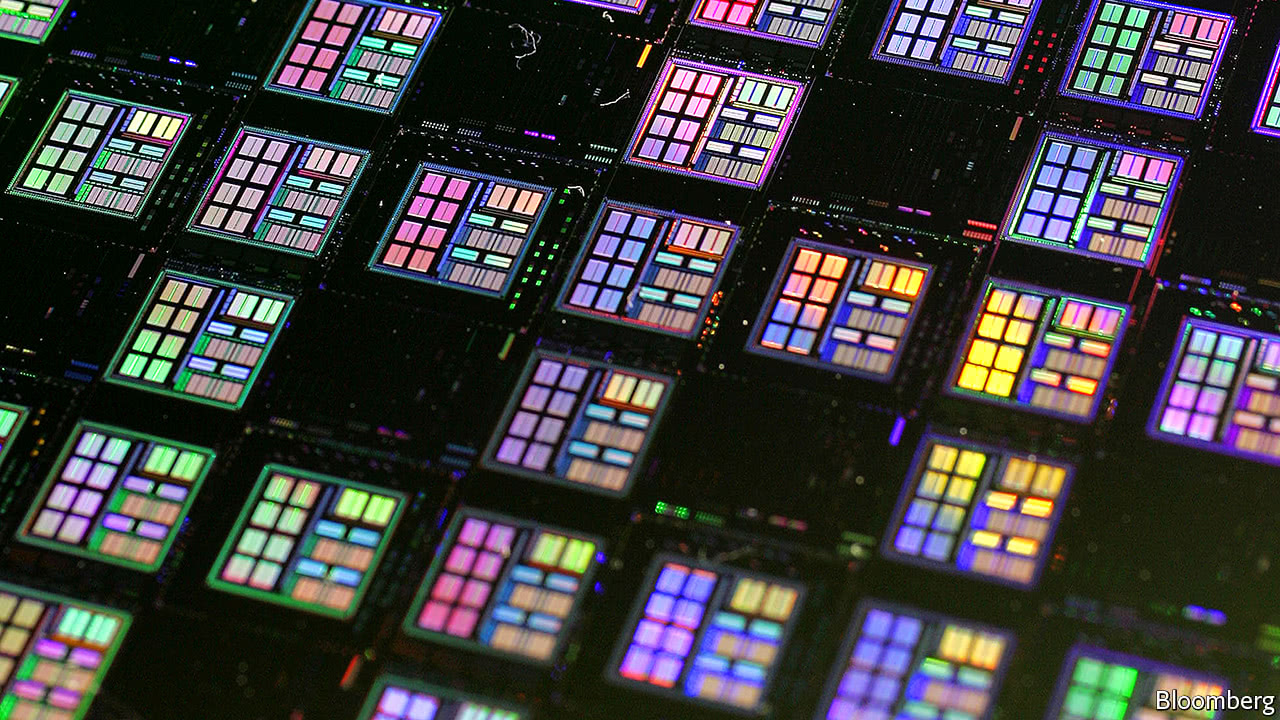

N3 firmy TSMC posiada komórkę bitową SRAM o wielkości 0,0199 µm², która jest tylko o ~5% mniejsza w porównaniu do komórki bitowej SRAM N5 o wielkości 0,021 µm². Gorzej jest z odświeżonym N3E, gdyż posiada on komórkę bitową SRAM o wielkości 0,021 µm² (co w przybliżeniu przekłada się na 31,8 Mib/mm²), co oznacza całkowity brak skalowania w porównaniu z N5. Tymczasem Intel 4 (pierwotnie nazywany 7nm EUV) zmniejsza rozmiar komórek bitowych SRAM do 0,024 µm² z 0,0312 µm² w przypadku Intela 7 (wcześniej znanego jako 10nm Enhanced SuperFin), nadal mówimy o czymś w rodzaju 27,8 Mib/mm², czyli nieco mniej niż SRAM HD TSMC.

Nowoczesne procesory, układy GPU i SoC wykorzystują mnóstwo pamięci SRAM do różnych pamięci podręcznych, ponieważ przetwarzają mnóstwo danych, a pobieranie danych z pamięci jest niezwykle nieefektywne, zwłaszcza w przypadku różnych obciążeń związanych ze sztuczną inteligencją (AI) i uczeniem maszynowym (ML). Ale nawet procesory ogólnego przeznaczenia, układy graficzne i procesory aplikacyjne dla smartfonów są obecnie wyposażone w ogromne pamięci podręczne: Ryzen 9 7950X firmy AMD posiada łącznie 81 MB pamięci podręcznej, natomiast AD102 firmy Nvidia wykorzystuje co najmniej 123 MB pamięci SRAM dla różnych pamięci podręcznych.

TSMC planuje wprowadzić swoją zoptymalizowaną pod kątem gęstości technologię procesową N3S, która obiecuje skurczyć rozmiar komórek bitowych SRAM w porównaniu do N5, ale ma to nastąpić około 2024 roku i zastanawiamy się, czy ta zapewni wystarczającą wydajność logiczną dla układów projektowanych przez AMD, Apple, Nvidię i Qualcomm.

Jednym ze sposobów na złagodzenie spowolnienia skalowania obszaru SRAM pod względem kosztów jest projektowanie wielochipletowe i rozdzielanie większych pamięci podręcznych na osobne układy wykonane na tańszym węźle. Jest to coś, co AMD robi ze swoim 3D V-Cache, choć z nieco innego powodu. Innym sposobem jest wykorzystanie alternatywnych technologii pamięci, takich jak eDRAM czy FeRAM dla pamięci podręcznej, choć te ostatnie mają swoje własne osobliwości.