TSMC podobno opracowuje opakowanie na poziomie panelu, kolejną nową technologię pakowania chipów

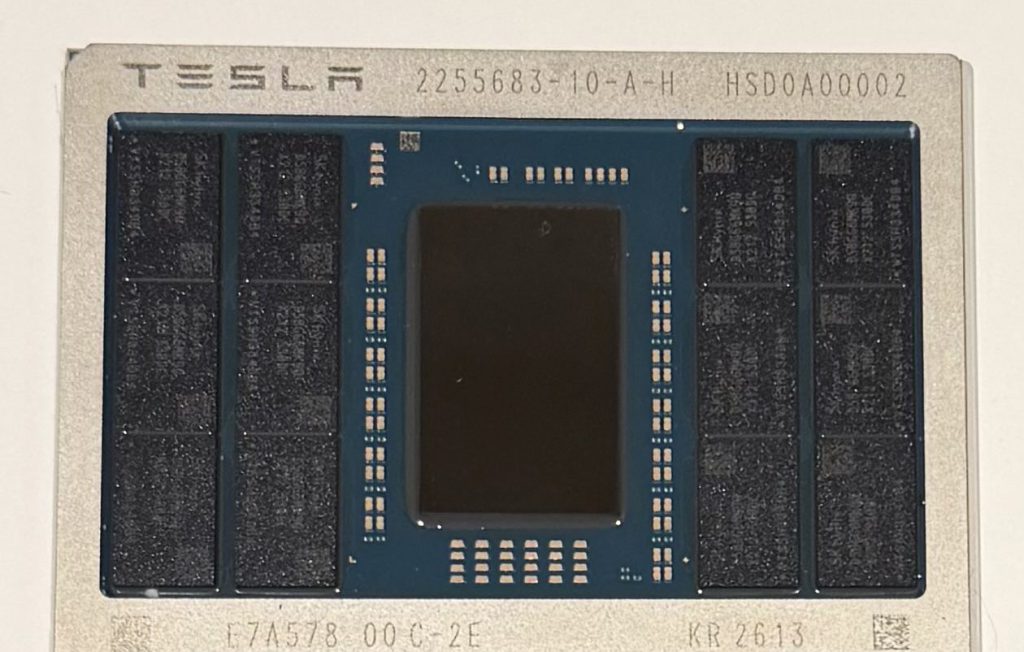

TSMC bada nową zaawansowaną technologię pakowania chipów, która wykorzystuje prostokątne podłoża przypominające panele, zamiast tradycyjnych okrągłych wafli, które są obecnie w użyciu.

Jak donosi Nikkei Asia, technologia ta pozwala na umieszczenie większej liczby chipów na jednym podłożu, odpowiadając na przyszłe trendy popytu napędzane przez sztuczną inteligencję. Chociaż badania są wciąż na wczesnym etapie i osiągnięcie masowej produkcji może zająć kilka lat, może stanowić to znaczącą zmianę technologiczną dla TSMC.

Według doniesień, TSMC eksperymentuje obecnie z prostokątnymi podłożami o wymiarach 515 mm na 510 mm, zapewniając ponad trzykrotnie większą powierzchnię użytkową w porównaniu do obecnych 12-calowych wafli, a tym samym może lepiej odpowiadać zapotrzebowaniu na chipsety AI.

W odpowiedzi na zapytanie Nikkei, TSMC stwierdziło, że firma uważnie monitoruje postępy i rozwój zaawansowanych technologii pakowania, w tym pakowania na poziomie panelu.

TSMC wstrzymuje budowę fabryki Chia-Yi z powodu znalezienia reliktu