TSMC przedstawiło plany rozwoju – zmiany w technologii pakowania chipów. Skorzysta na tym przede wszystkim AMD.

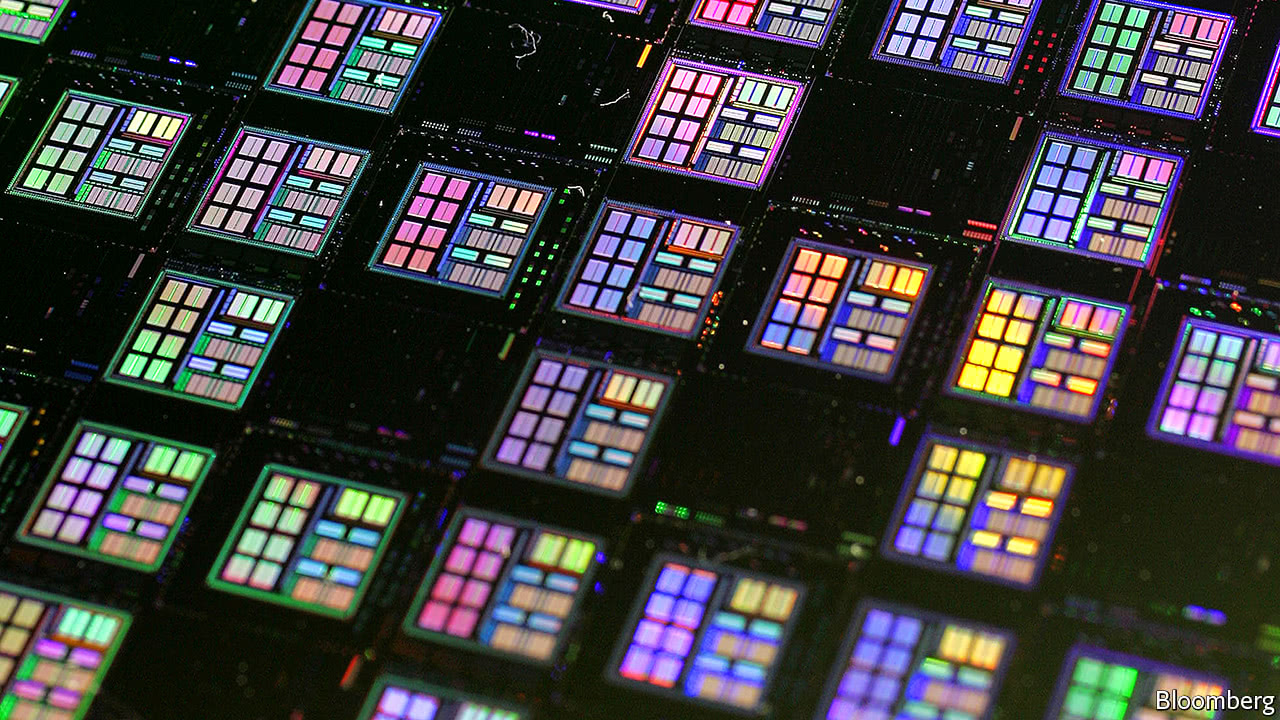

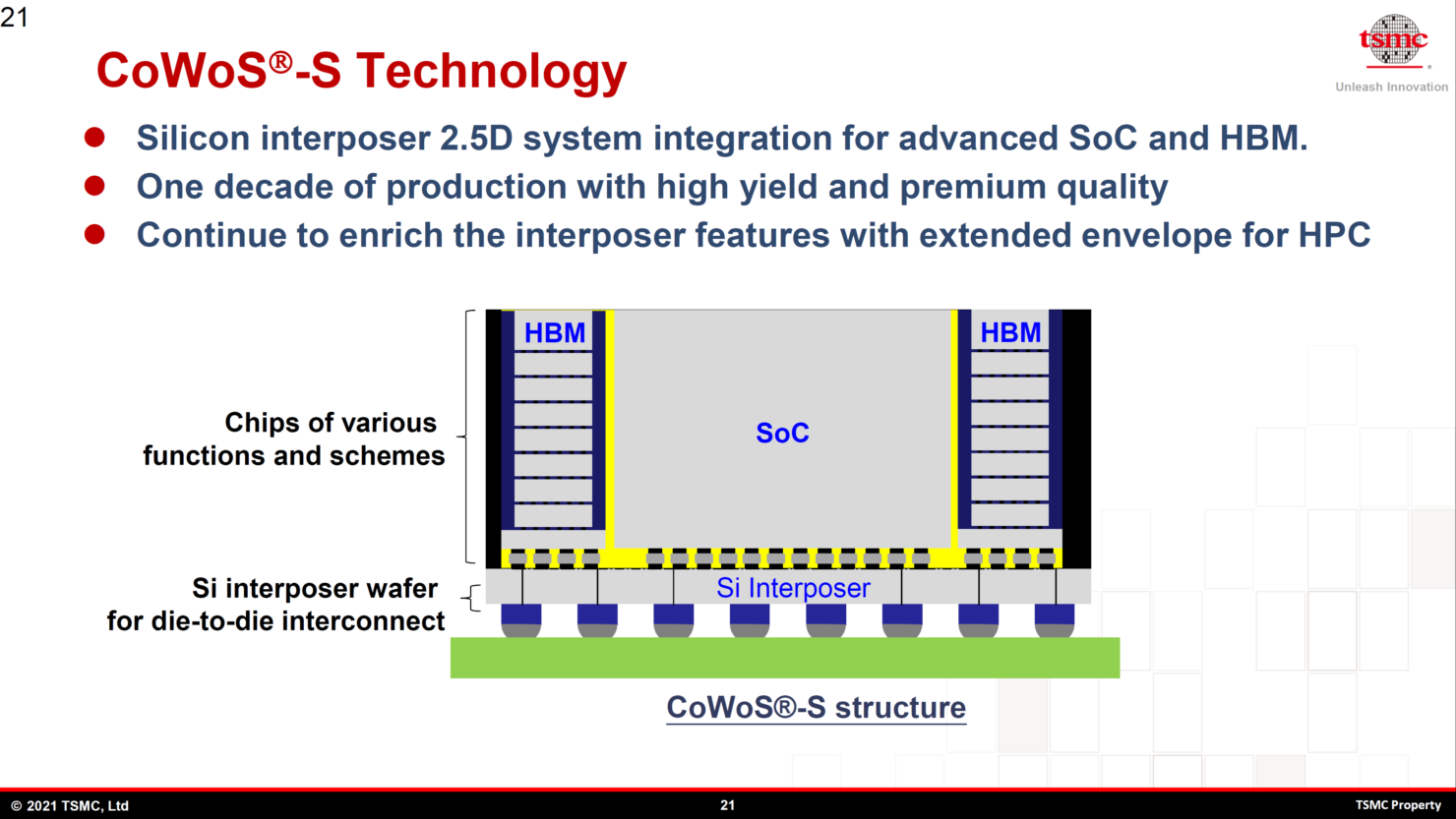

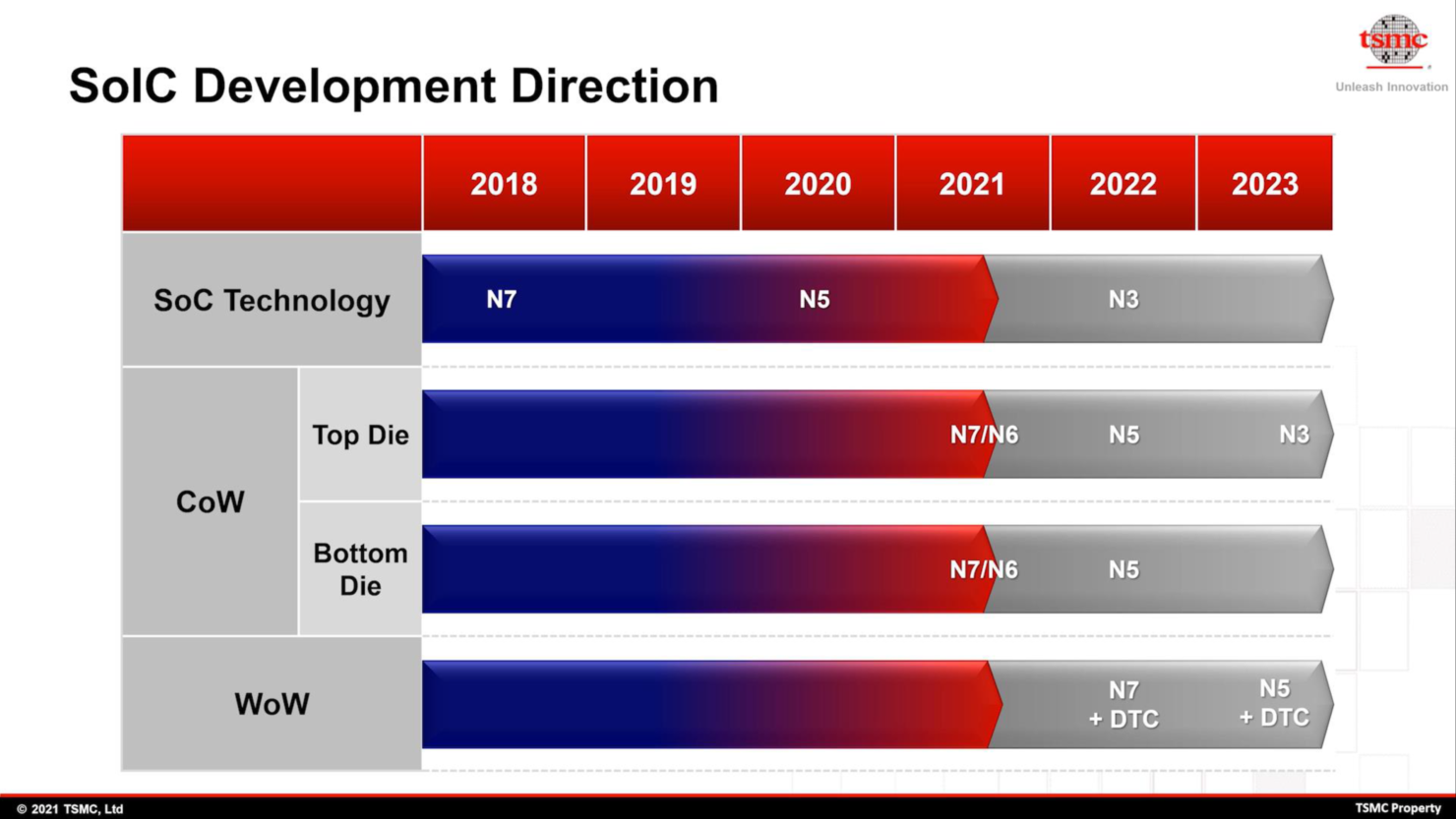

Firma TSMC przedstawiła plan rozwoju zaawansowanych technologii pakowania i zaprezentowała rozwiązania CoWoS (Chip-on-Wafer-on-Substrate) nowej generacji, które są gotowe na architektury bazujące na chipletach i pamięci nowej generacji.

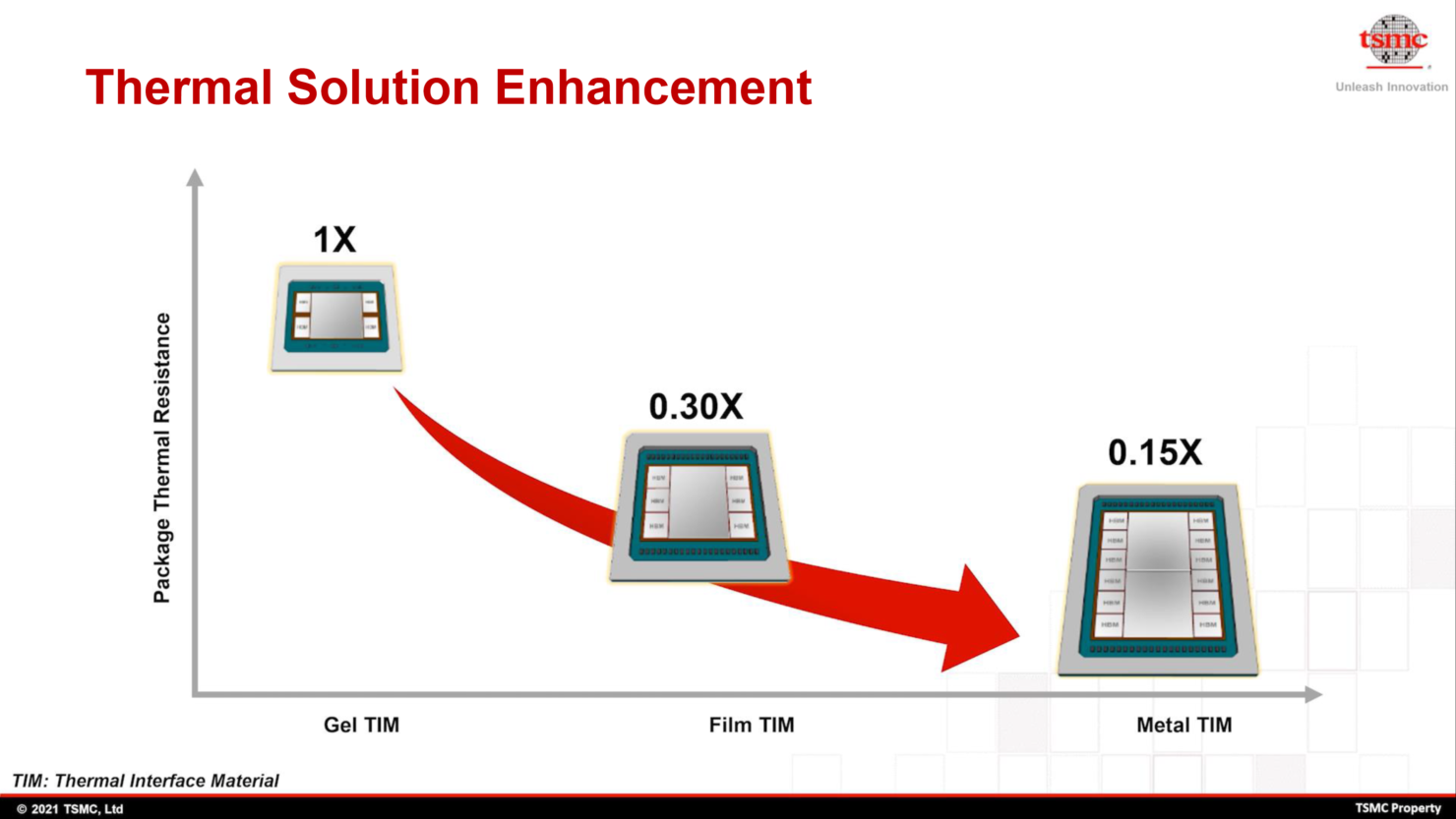

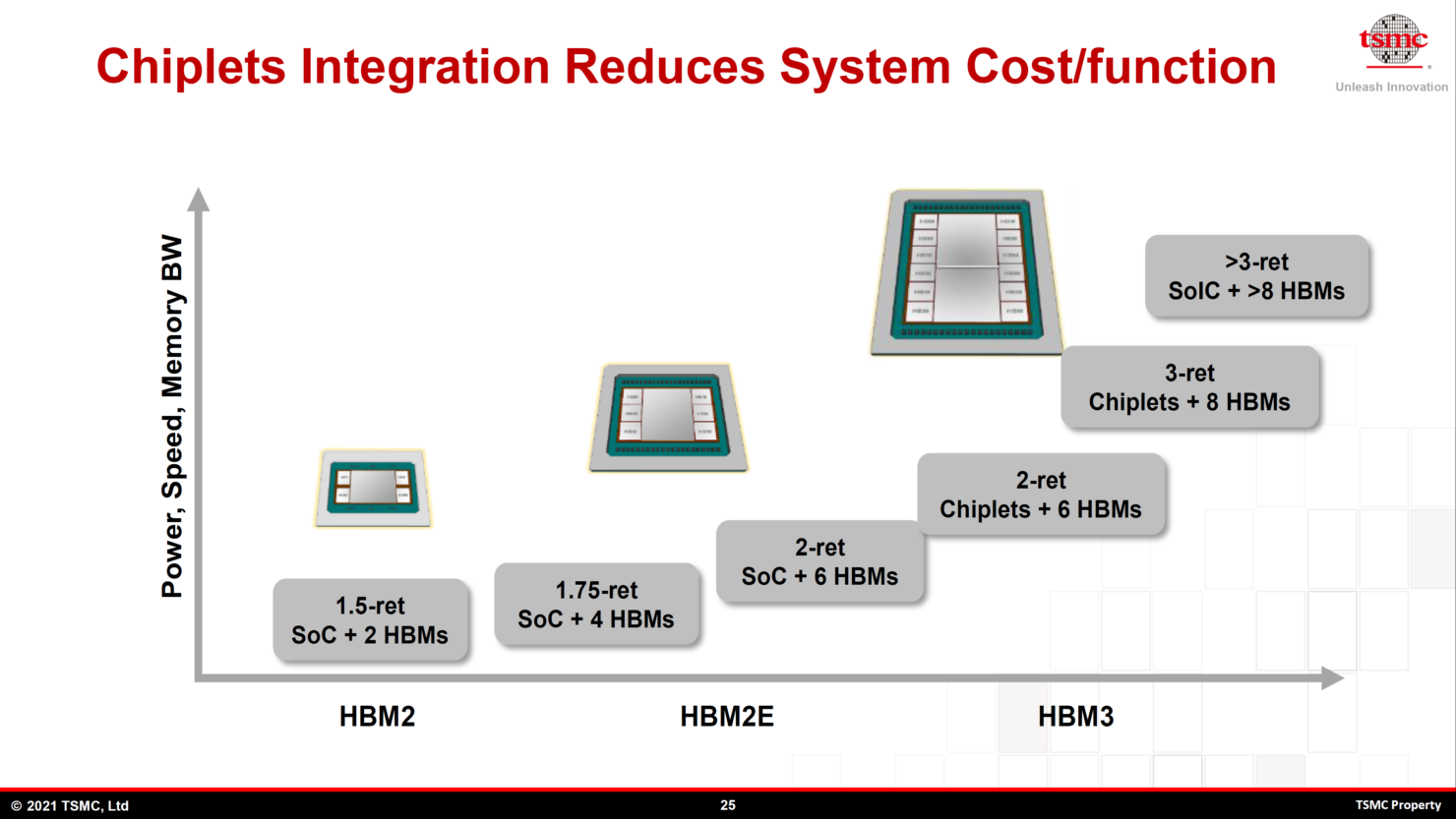

Tajwański wytwórca w ciągu dekady wprowadził pięć różnych generacji pakietów CoWoS (Chip-on-Wafer-on-Substrate). Firma spodziewa się wprowadzić swoje rozwiązanie pakowania SoC CoWoS Gen 5 jeszcze w tym roku. Zdaniem producenta, zwiększy to liczbę tranzystorów 20-krotnie w porównaniu z rozwiązaniem trzeciej generacji. Nowy pakiet będzie wyposażony w 3-krotny wzrost obszaru pośredniczącego, 8 stosów HBM2e o pojemności do 128 GB, zupełnie nowe rozwiązanie TSV i nowy TIM. Kto wykorzysta nowe możliwości produkcyjne TSMC?

Najbardziej godnym uwagi rozwiązaniem, które wykorzysta technologię pakowania Gen 5 od TSMC, jest procesor graficzny AMD MI200 „Aldebaran”. Procesor graficzny AMD Aldebaran będzie budowany zgodnie z architekturą CDNA 2 AMD.

Do 6. generacji TSMC będzie mieć większy obszar siatki, aby zintegrować więcej chipletów i więcej pakietów DRAM. Projekt pakietu nie został jeszcze sfinalizowany przez TSMC.

W efekcie, otwiera to wiele nowych możliwości dla klientów TSMC, szczególnie dla AMD. Intel wprawdzie też wykorzystuje częśc mocy produkcyjnych TSMC, ale prawdopodobnie przeważy tu własna wizja pakowania układów. AMD natomiast może skorzystać z nowej metody by integrować, wyraźnie “lubianą” przez firmę, pamięci HBM kolejnych generacji, w swoich SoC.

https://itreseller.pl/naukowcy-wykorzystuja-mozliwosci-mieszanej-rzeczywistosci-i-urzadzenia-microsoft-hololens-program-holomedicine-nuhs-bada-w-jaki-sposob-hololens-moglyby-byc-stosowane-w-roznych-sytuacjach-klinicz/